- 您現在的位置:買賣IC網 > PDF目錄373916 > AD7769AP (ANALOG DEVICES INC) LC2MOS Analog I/O Port PDF資料下載

參數資料

| 型號: | AD7769AP |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | LC2MOS Analog I/O Port |

| 中文描述: | 2-CH 8-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, PQCC28 |

| 封裝: | PLASTIC, LCC-28 |

| 文件頁數: | 12/16頁 |

| 文件大小: | 265K |

| 代理商: | AD7769AP |

AD7769

–12–

REV. A

Conversion is initiated on the selected AD7769 ADC channel

using a single I/O instruction, <OUT ADC, A>. T he processor

then polls

INT

until it goes low before reading the conversion

result using an <IN A, ADC> instruction. Writing data to the rel-

evant AD7769 DAC consists of an <OUT DAC, A> instruction.

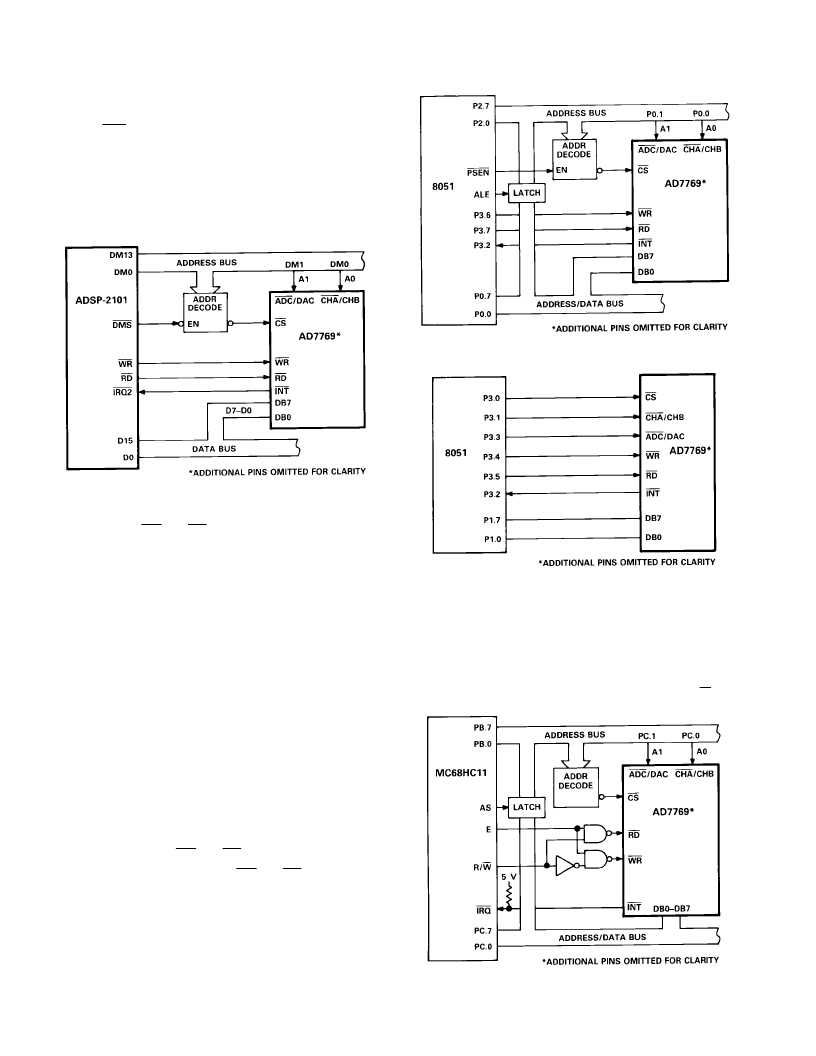

AD7769–ADSP-2101 Interface

Figure 19 shows a typical interface to the DSP microcomputer,

the ADSP-2101. T he ADSP-2101 is optimized for high speed

numeric processing tasks.

Figure 19. AD7769 to ADSP-2101 Interface

Because the instruction cycle of the ADSP-2101 is very fast

(80 ns cycle), the

WR

and

RD

pulses must be stretched out to

suit the AD7769. T his is easily achieved as the ADSP-2101

memory interface supports slower memories and memory-

mapped peripherals (i.e., AD7769) with a programmable wait

state generation capability. A number of wait states, from 0 to 7,

can be specified for each memory interface. One wait state is

sufficient for the interface to the AD7769.

AD7769–8051 Interface

A choice of two interface modes are available to the 8051

microcomputer.

Figure 20 shows a typical interface to the 8051 processor bus. It

is suitable for the maximum 8051 clock frequency of 12 MHz.

In this interface mode, Port 0 provides the multiplexed low or-

der address and data bus and Port 2 provides the high order ad-

dress bus (A

8

–A

15

).

Figure 21 shows the AD7769 interfaced to the 8051 parallel I/O

ports. T his interface circuit is simpler to implement than the

previous interface to the processor bus, but, in general, the

maximum data throughput rate is much slower (for the same

clock frequencies). In addition to its simplicity, the interface to

the parallel I/O ports versus the processor bus allows indepen-

dent control of both the

WR

and

RD

inputs to the AD7769.

For example, the 8051 can set both

WR

and

RD

low at the

same time. T his permits data from the last ADC conversion to

be written directly from the ADC register into the selected DAC

register (see Logic T ruth T able). T his allows very fast transfer

of data from the ADC to the DAC and is a useful feature for

some applications such as a fast, programmable, infinite sample-

and-hold function.

Figure 20. AD7769 to 8051 (Processor Bus) Interface

Figure 21. AD7769 to 8051 (Parallel l/O Ports) Interface

AD7769–MC68HC11 Interface

Figure 22 shows a typical interface between the AD7769 and the

MC68HC11 microcomputer. T his interface is designed for the

maximum MC68HC11 clock speed of 8.4 MHz. T he microcom-

puter is operated in the expanded multiplexed mode, with the

AD7769 as a memory mapped peripheral. T he expansion bus is

made up of Ports B and C, and control signals AS and R/

W

.

Figure 22. AD7769 to MC68HC11 Interfaced

相關PDF資料 |

PDF描述 |

|---|---|

| AD7769JN | LC2MOS Analog I/O Port |

| AD7769JP | LC2MOS Analog I/O Port |

| AD7773 | LC MOS COMPLETE EMBEDDED SERVO FRONT ENDS FOR HDD |

| AD7775 | LC MOS COMPLETE EMBEDDED SERVO FRONT ENDS FOR HDD |

| AD7776 | LC2MOS, High Speed 1-, 4- & 8-Channel 10-Bit ADCs |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD7769JN | 制造商:AD 制造商全稱:Analog Devices 功能描述:LC2MOS Analog I/O Port |

| AD7769JP | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| AD7769JP-REEL | 制造商:Rochester Electronics LLC 功能描述:- Tape and Reel |

| AD7769KN | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:CODEC, Single |

| AD7769KP | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:CODEC, Single |

發布緊急采購,3分鐘左右您將得到回復。