- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373918 > AD7824BQ (ANALOG DEVICES INC) 1.2V, 12 Bit 200KSPS, Serial ADC 6-SOT-23 -40 to 85 PDF資料下載

參數(shù)資料

| 型號(hào): | AD7824BQ |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | 1.2V, 12 Bit 200KSPS, Serial ADC 6-SOT-23 -40 to 85 |

| 中文描述: | 4-CH 8-BIT FLASH METHOD ADC, PARALLEL ACCESS, CDIP24 |

| 封裝: | HERMETIC SEALED, CERDIP-24 |

| 文件頁(yè)數(shù): | 7/16頁(yè) |

| 文件大小: | 270K |

| 代理商: | AD7824BQ |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)當(dāng)前第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)

AD7824/AD7828

REV. F

–7–

INPUT CURRENT

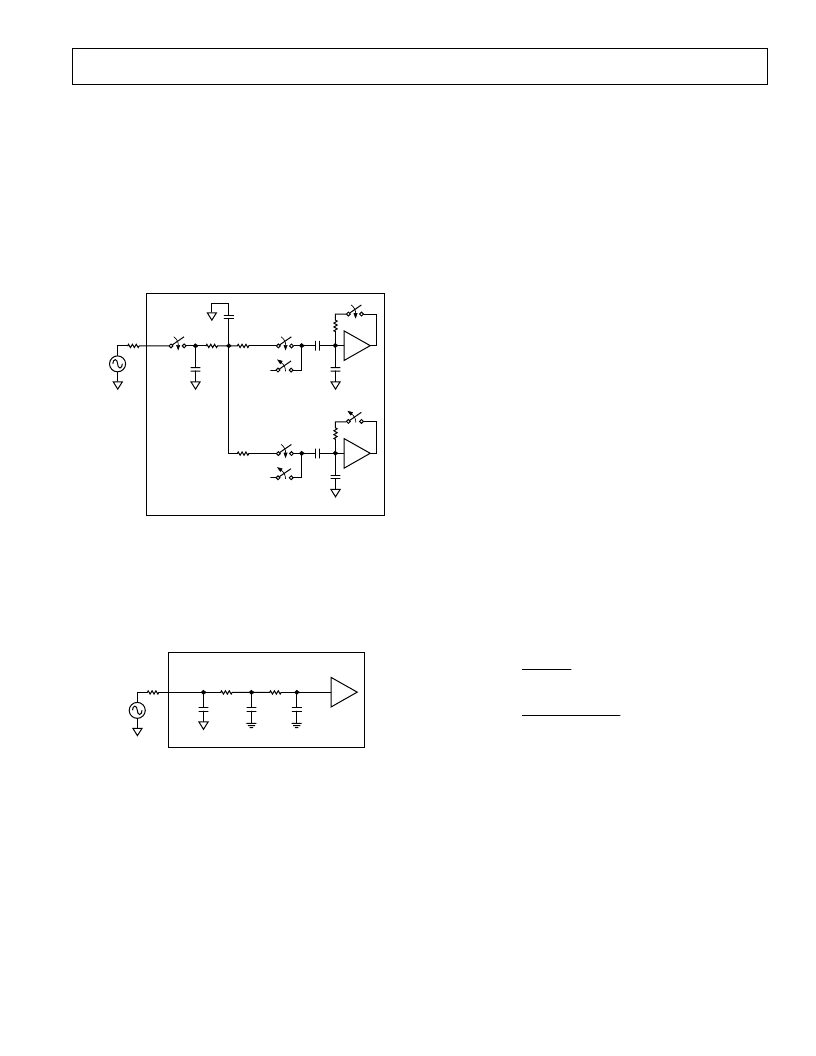

Due to the novel conversion techniques employed by the AD7824/

AD7828, the analog input behaves somewhat differently than in

conventional devices. The ADC’s sampled-data comparators

take varying amounts of input current depending on which cycle

the conversion is in.

The equivalent input circuit of the AD7824/AD7828 is shown

in Figure 8. When a conversion starts (

CS

and

RD

going low),

all input switches close, and the selected input channel is con-

nected to the most significant and least significant comparators.

Therefore, the analog input is simultaneously connected to

31 input capacitors of 1 pF each.

1pF

1pF

15LSB

COMPARATORS

1pF

1pF

16MSB

COMPARATORS

TO LS

LADDER

R

ON

R

ON

R MUX

C

12pF

C

S

2pF

R

S

AIN1

TO MS

LADDER

V

IN

AD7824/

AD7828

Figure 8. AD7824/AD7828 Equivalent Input Circuit

The input capacitors must charge to the input voltage through

the on resistance of the analog switches (about 3 k

to 6 k

). In

addition, about 14 pF of input stray capacitance must be charged.

The analog input for any channel can be modelled as an RC

network, as shown in Figure 9. As R

S

increases, it takes longer

for the input capacitance to charge.

R

ON

350

R MUX

800

C

12pF

R

S

V

IN

C

S2

2pF

31pF

AIN1

Figure 9. RC Network Model

The time for which the input comparators track the analog input

is approximately 1

μ

s at the start of conversion. Because of input

transients on the analog inputs, it is recommended that a source

impedance no greater than 100

be connected to the analog

inputs. The output impedance of an op amp is equal to the open

loop output impedance divided by the loop gain at the frequency of

interest. It is important that the amplifier driving the AD7824/

AD7828 analog inputs have sufficient loop gain at the input signal

frequency as to make the output impedance low.

Suitable op amps for driving the AD7824/AD7828 are the AD544

or AD644.

INHERENT SAMPLE-HOLD

A major benefit of the AD7824’s and AD7828’s analog input

structure is its ability to measure a variety of high speed signals

without the help of an external sample-and-hold. In a conven-

tional SAR type converter, regardless of its speed, the input

must remain stable to at least 1/2 LSB throughout the conversion

process if rated accuracy is to be maintained. Consequently, for

many high speed signals, this signal must be externally sampled

and held stationary during the conversion. The AD7824/AD7828

input comparators, by nature of their input switching, inherently

accomplish this sample-and-hold function. Although the conver-

sion time for AD7824/AD7828 is 2

μ

s, the time for which any

selected analog input must be 1/2 LSB stable is much smaller.

The AD7824/AD7828 tracks the selected input channel for

approximately 1

μ

s after conversion start. The value of the analog

input at that instant (1

μ

s from conversion start) is the measured

value. This value is then used in the least significant flash to

generate the lower four bits of data.

SINUSOIDAL INPUTS

The AD7824/AD7828 can measure input signals with slew rates

as high as 157 mV/

μ

s to the rated specifications. This means that

the analog input frequency can be up to 10 kHz without the aid

of an external sample-and-hold. Furthermore, the AD7828 can

measure eight 10 kHz signals without a sample-and-hold. The

Nyquist criterion requires that the sampling rate be twice the

input frequency (i.e., 2

×

10 kHz). This requires an ideal anti-

aliasing filter with an infinite roll-off. To ease the problem of

antialiasing filter design, the sampling rate is usually much greater

than the Nyquist criterion. The maximum sampling rate (F

MAX

)

for the AD7824/AD7828 can be calculated as follows:

F

t

t

MAX

CRD

P

=

+

1

F

E

E

kHz

MAX

=

+

=

1

2

6

0 5

.

6

400

–

–

t

CRD

= AD7824/AD7828 Conversion Time

t

P

= Minimum Delay Between Conversion

This permits a maximum sampling rate of 50 kHz for each of

the eight channels when using the AD7828 and 100 kHz for

each of the four channels when using the AD7824.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD7828LRS | LC2MOS High Speed 4- & 8-Channel 8-Bit ADCs |

| AD7834 | 14-Bit Quad DAC(14位四D/A轉(zhuǎn)換器) |

| AD7835 | 14-Bit Quad DAC(14位四D/A轉(zhuǎn)換器) |

| AD7837AR | LC2MOS Complete, Dual 12-Bit MDACs |

| AD7837BN | LC2MOS Complete, Dual 12-Bit MDACs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD7824BQ/+ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Single-Ended Data Acquisition System |

| AD7824CQ | 功能描述:IC ADC 8BIT LC2MOS 4CH HS 24CDIP RoHS:否 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 模數(shù)轉(zhuǎn)換器 系列:- 標(biāo)準(zhǔn)包裝:1 系列:- 位數(shù):14 采樣率(每秒):83k 數(shù)據(jù)接口:串行,并聯(lián) 轉(zhuǎn)換器數(shù)目:1 功率耗散(最大):95mW 電壓電源:雙 ± 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:28-DIP(0.600",15.24mm) 供應(yīng)商設(shè)備封裝:28-PDIP 包裝:管件 輸入數(shù)目和類型:1 個(gè)單端,雙極 |

| AD7824CQ/+ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Single-Ended Data Acquisition System |

| AD7824KCWG | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Single-Ended Data Acquisition System |

| AD7824KN | 功能描述:IC ADC 8BIT LC2MOS 4CH HS 24DIP RoHS:否 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 模數(shù)轉(zhuǎn)換器 系列:- 標(biāo)準(zhǔn)包裝:1 系列:- 位數(shù):14 采樣率(每秒):83k 數(shù)據(jù)接口:串行,并聯(lián) 轉(zhuǎn)換器數(shù)目:1 功率耗散(最大):95mW 電壓電源:雙 ± 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:28-DIP(0.600",15.24mm) 供應(yīng)商設(shè)備封裝:28-PDIP 包裝:管件 輸入數(shù)目和類型:1 個(gè)單端,雙極 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。