- 您現在的位置:買賣IC網 > PDF目錄373920 > AD7854BR (ANALOG DEVICES INC) 3 V to 5 V Single Supply, 200 kSPS 12-Bit Sampling ADCs PDF資料下載

參數資料

| 型號: | AD7854BR |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | 3 V to 5 V Single Supply, 200 kSPS 12-Bit Sampling ADCs |

| 中文描述: | 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, PDSO28 |

| 封裝: | SOIC-28 |

| 文件頁數: | 9/28頁 |

| 文件大小: | 264K |

| 代理商: | AD7854BR |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

AD7854/AD7854L

REV. B

–

9

–

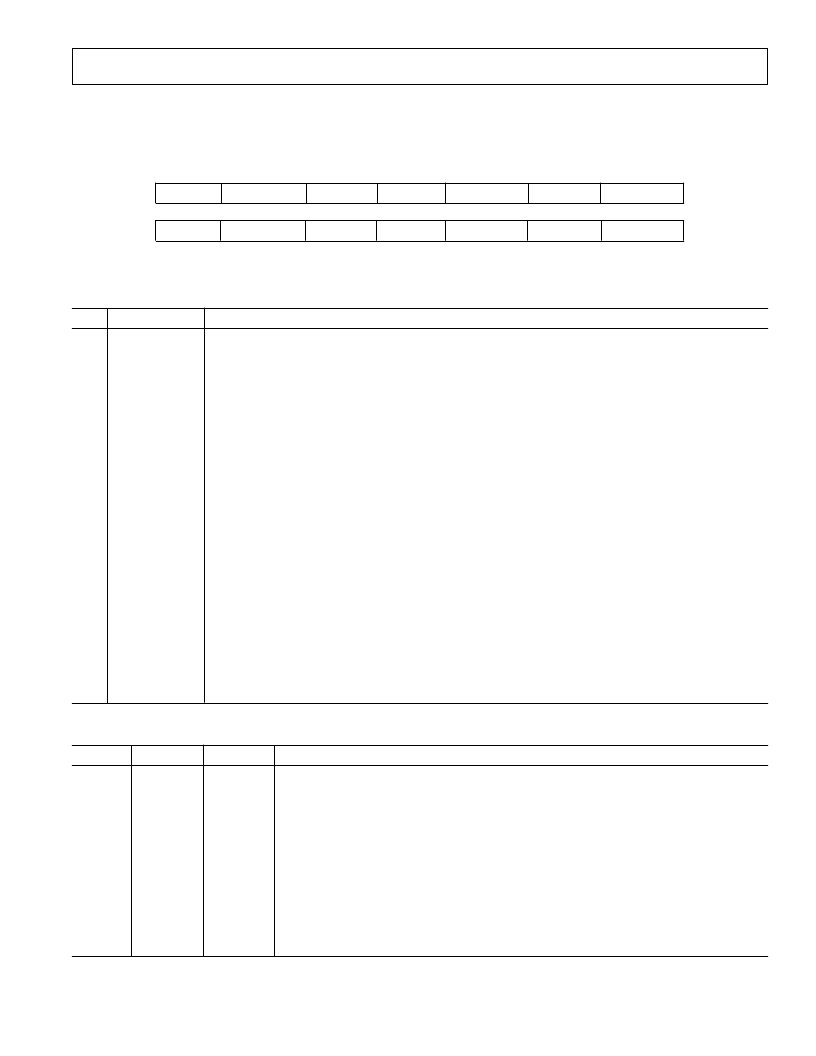

CONTROL REGISTER

The arrangement of the control register is shown below. The control register is a write only register and contains 14 bits of data. The

control register is selected by putting two 1s in ADDR1 and ADDR0. The function of the bits in the control register is described

below. The power-up status of all bits is 0.

MSB

ZERO

ZERO

ZERO

ZERO

PMGT1

PMGT0

RDSLT1

RDSLT0

AMODE

CONVST

CALMD

CALSLT1

CALSLT0

STCAL

LSB

Control Register Bit Function Description

Bit

Mnemonic

Comment

13

12

11

10

9

8

7

6

5

ZERO

ZERO

ZERO

ZERO

PMGT1

PMGT0

RDSLT1

RDSLT0

AMODE

These four bits must be set to 0 when writing to the control register.

Power Management Bits. These two bits are used for putting the part into various power-down modes

(See

Power-Down

section for more details).

Theses two bits determine which register is addressed for the read operations. See Table II.

Analog Mode Bit. This pin allows two different analog input ranges to be selected. A logic 0 in this bit

position selects range 0 to V

REF

(i.e., AIN(+)

–

AIN(

–

) = 0 to V

REF

). In this range AIN(+) cannot go

below AIN(

–

) and AIN(

–

) cannot go below AGND and data coding is straight binary. A logic 1 in this

bit position selects range

–

V

REF

/2 to +V

REF

/2 (i.e., AIN(+)

–

AIN(

–

) =

–

V

REF

/2 to +V

REF

/2). AIN(+)

cannot go below AGND, so for this range, AIN(

–

) needs to be biased to at least +V

REF

/2 to allow

AIN(+) to go as low as AIN(

–

)

–

V

REF

/2 V. Data coding is twos complement for this range.

Conversion Start Bit. A logic one in this bit position starts a single conversion, and this bit is automati-

cally reset to 0 at the end of conversion. This bit may also used in conjunction with system calibration

(see Calibration section).

Calibration Mode Bit. A 0 here selects self-calibration and a 1 selects a system calibration (see Table III).

Calibration Selection Bits and Start Calibration Bit. These bits have two functions.

With the STCAL bit set to 1, the CALSLT1 and CALSLT0 bits determine the type of calibration per-

formed by the part (see Table III). The STCAL bit is automatically reset to 0 at the end of calibration.

With the STCAL bit set to 0, the CALSLT1 and CALSLT0 bits are decoded to address the calibration

register for read/write of calibration coefficients (see section on the calibration registers for more details).

4

CONVST

3

2

1

0

CALMD

CALSLT1

CALSLT0

STCAL

Table III. Calibration Selection

CALMD

CALSLT1

CALSLT0

Calibration Type

0

0

0

A

full internal calibration

is initiated. First the internal DAC is calibrated, then the

internal gain error and finally the internal offset error are removed. This is the default setting.

First the

internal gain error

is removed, then the

internal offset error

is removed.

The

internal offset error

only is calibrated out.

The

internal gain error

only is calibrated out.

A

full system calibration

is initiated. First the internal DAC is calibrated, followed by the

system gain error calibration, and finally the system offset error calibration.

First the

system gain error

is calibrated out followed by the

system offset error

.

The

system offset error

only is removed.

The

system gain error

only is removed.

0

0

0

1

0

1

1

0

1

0

1

0

1

1

1

0

1

1

1

0

1

相關PDF資料 |

PDF描述 |

|---|---|

| AD7854AR | 3 V to 5 V Single Supply, 200 kSPS 12-Bit Sampling ADCs |

| AD7854L | 12-Bit Sampling ADC(單電源,200kSPS 12位采樣A/D轉換器) |

| AD7854 | 12-Bit Sampling ADC(單電源,200kSPS 12位采樣A/D轉換器) |

| AD7858LARS | 3 V to 5 V Single Supply, 200 kSPS 8-Channel, 12-Bit Sampling ADC |

| AD7858BN | 3 V to 5 V Single Supply, 200 kSPS 8-Channel, 12-Bit Sampling ADC |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD7854BR-REEL | 制造商:Analog Devices 功能描述:ADC Single SAR 200ksps 12-bit Parallel 28-Pin SOIC W T/R |

| AD7854BRZ | 功能描述:IC ADC 12BIT PARALLEL LP 28-SOIC RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 產品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:2,500 系列:- 位數:12 采樣率(每秒):3M 數據接口:- 轉換器數目:- 功率耗散(最大):- 電壓電源:- 工作溫度:- 安裝類型:表面貼裝 封裝/外殼:SOT-23-6 供應商設備封裝:SOT-23-6 包裝:帶卷 (TR) 輸入數目和類型:- |

| AD7854L | 制造商:AD 制造商全稱:Analog Devices 功能描述:3 V to 5 V Single Supply, 200 kSPS 12-Bit Sampling ADCs |

| AD7854LAQ | 制造商:Rochester Electronics LLC 功能描述:12 BIT SINGLE CHANNEL PARALLEL ADC I.C. - Bulk |

發布緊急采購,3分鐘左右您將得到回復。