- 您現在的位置:買賣IC網 > PDF目錄373921 > AD7863ARS-3 (ANALOG DEVICES INC) Simultaneous Sampling Dual 175 kSPS 14-Bit ADC PDF資料下載

參數資料

| 型號: | AD7863ARS-3 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | Simultaneous Sampling Dual 175 kSPS 14-Bit ADC |

| 中文描述: | 4-CH 14-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, PDSO28 |

| 封裝: | MO-150AH, SSOP-28 |

| 文件頁數: | 10/18頁 |

| 文件大小: | 207K |

| 代理商: | AD7863ARS-3 |

AD7863

–

10

–

REV. A

Gain error can be adjusted at either the first code transition (ADC

negative full scale) or the last code transition (ADC positive full

scale). The trim procedures for both cases are as follows:

Positive Full-Scale Adjust (-10 Version)

Apply a voltage of +9.9927 V (FS/2

–

1 LSBs) at V

1

. Adjust R2

until the ADC output code flickers between 01 1111 1111 1110

and 01 1111 1111 1111.

Negative Full-Scale Adjust (-10 Version)

Apply a voltage of

–

9.9976 V (

–

FS + 1 LSB) at V

1

and adjust

R2 until the ADC output code flickers between 10 0000 0000

0000 and 10 0000 0000 0001.

An alternative scheme for adjusting full-scale error in systems

that use an external reference is to adjust the voltage at the V

REF

pin until the full-scale error for any of the channels is adjusted

out. The good full-scale matching of the channels will ensure

small full-scale errors on the other channels.

TIMING AND CONTROL

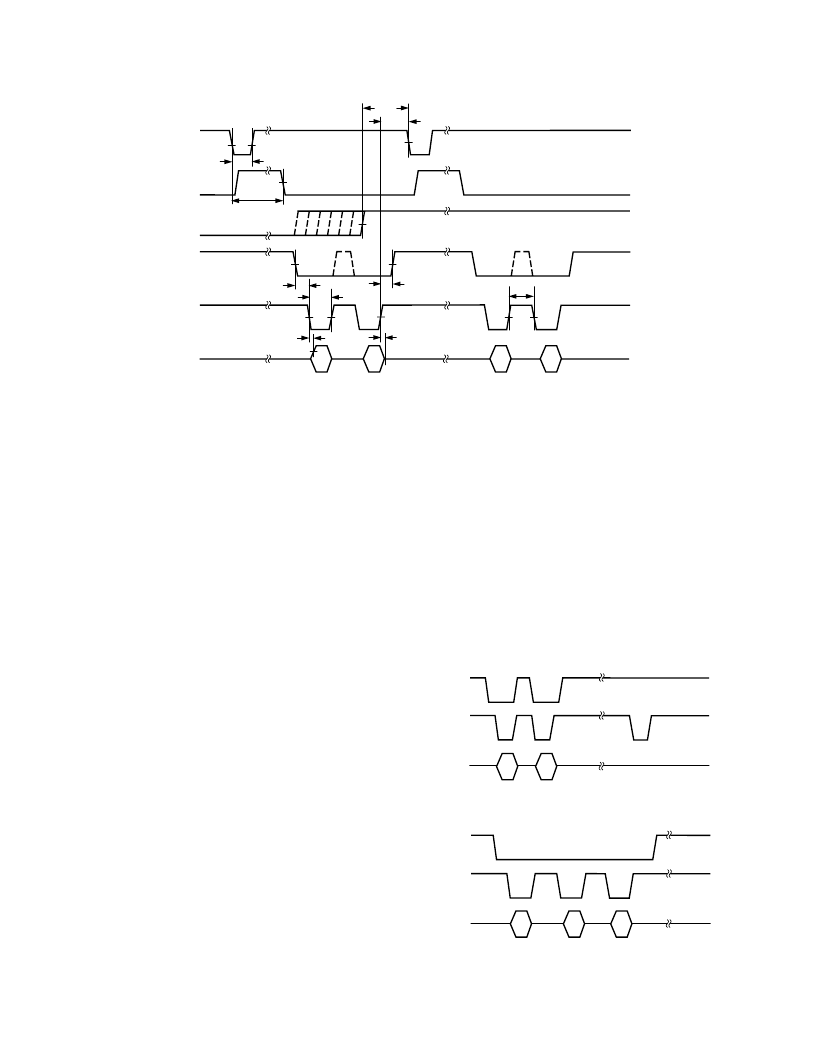

Figure 5a shows the timing and control sequence required to

obtain optimum performance (Mode 1) from the AD7863. In

the sequence shown, a conversion is initiated on the falling edge

of

CONVST

. This places both track/holds into hold simulta-

neously and new data from this conversion is available in the

output register of the AD7863 5.2

μ

s later. The BUSY signal

indicates the end of conversion and at this time the conversion

results for both channels are available to be read. A second

conversion is then initiated. If the multiplexer select A0 is low,

the first and second read pulses after the first conversion ac-

cesses the result from Channel A (V

A1

and V

A2

respectively).

The third and fourth read pulses, after the second conversion

and A0 high, accesses the result from Channel B (V

B1

and V

B2

respectively). A0

’

s state can be changed any time after the

CONVST

goes high, i.e., track/holds into hold and 500 ns prior

to the next falling edge of

CONVST

. Note that A0 should not

be changed during conversion if the nonselected channels have

negative voltages applied to them which are outside the input

range of the AD7863, as this will affect the conversion in

progress. Data is read from the part via a 14-bit parallel data bus

with standard

CS

and

RD

signal, i.e., the read operation con-

sists of a negative going pulse on the

CS

pin combined with two

negative going pulses on the

RD

pin (while the

CS

is low),

accessing the two 14-bit results. Once the read operation has

taken place, a further 400 ns should be allowed before the next

falling edge of

CONVST

to optimize the settling of the track/

hold amplifier before the next conversion is initiated. The

achievable throughput rate for the part is 5.2

μ

s (conversion

time) plus 100 ns (read time) plus 0.4

μ

s (quiet time). This

results in a minimum throughput time of 5.7

μ

s (equivalent to a

throughput rate of 175 kHz).

Read Options

Apart from the Read Operation described above and displayed

in Figure 5a, other

CS

and

RD

combinations can result in dif-

ferent channels/inputs being read in different combinations.

Suitable combinations are shown in Figures 5b through 5d.

CS

RD

DATA

V

A1

V

A2

Figure 5b. Read Option A (A0 Is Low)

CS

RD

DATA

V

A1

V

A2

V

A1

Figure 5c. Read Option B (A0 Is Low)

t

3

t

5

t

4

V

A1

V

A2

V

B1

V

B2

CONVST

BUSY

A0

CS

RD

DATA

t

1

t

7

t

2

t

6

t

CONV

= 5.2 s

t

ACQ

t

8

Figure 5a. Mode 1 Timing Operation Diagram for High Sampling Performance

相關PDF資料 |

PDF描述 |

|---|---|

| AD7863AR-2 | RECTIFIER SCHOTTKY DUAL 30A 60V 275A-ifsm 0.7V-vf 1mA-ir TO-3P 30/TUBE |

| AD7863AR-3 | RECTIFIER SCHOTTKY DUAL 40A 40V 375A-ifsm 0.58V-vf 1mA-ir TO-3P 30/TUBE |

| AD7864AS-1 | VARISTOR 150V RMS 20MM RADIAL |

| AD7864BS-1 | SWITCH SLIDE DP3T RT ANG L=6MM |

| AD7864AS-2 | 4-Channel, Simultaneous Sampling, High Speed, 12-Bit ADC |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD7863ARS-3REEL | 功能描述:IC ADC 14BIT DUAL 2CH 28-SSOP RoHS:否 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1 系列:- 位數:14 采樣率(每秒):83k 數據接口:串行,并聯 轉換器數目:1 功率耗散(最大):95mW 電壓電源:雙 ± 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:28-DIP(0.600",15.24mm) 供應商設備封裝:28-PDIP 包裝:管件 輸入數目和類型:1 個單端,雙極 |

| AD7863ARS-3REEL7 | 功能描述:IC ADC 14BIT DUAL 2CH 28-SSOP RoHS:否 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1 系列:- 位數:14 采樣率(每秒):83k 數據接口:串行,并聯 轉換器數目:1 功率耗散(最大):95mW 電壓電源:雙 ± 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:28-DIP(0.600",15.24mm) 供應商設備封裝:28-PDIP 包裝:管件 輸入數目和類型:1 個單端,雙極 |

| AD7863ARSZ-10 | 功能描述:IC ADC 14BIT DUAL 2CHAN 28SSOP RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 其它有關文件:TSA1204 View All Specifications 標準包裝:1 系列:- 位數:12 采樣率(每秒):20M 數據接口:并聯 轉換器數目:2 功率耗散(最大):155mW 電壓電源:模擬和數字 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:48-TQFP 供應商設備封裝:48-TQFP(7x7) 包裝:Digi-Reel® 輸入數目和類型:4 個單端,單極;2 個差分,單極 產品目錄頁面:1156 (CN2011-ZH PDF) 其它名稱:497-5435-6 |

| AD7863ARSZ-101 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Simultaneous Sampling Dual 175 kSPS 14-Bit ADC |

| AD7863ARSZ-10REEL | 功能描述:IC ADC 14BIT DUAL 2CHAN 28SSOP RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1,000 系列:- 位數:12 采樣率(每秒):300k 數據接口:并聯 轉換器數目:1 功率耗散(最大):75mW 電壓電源:單電源 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:24-SOIC(0.295",7.50mm 寬) 供應商設備封裝:24-SOIC 包裝:帶卷 (TR) 輸入數目和類型:1 個單端,單極;1 個單端,雙極 |

發布緊急采購,3分鐘左右您將得到回復。