- 您現在的位置:買賣IC網 > PDF目錄373942 > AD8307AR-REEL (ANALOG DEVICES INC) Low Cost DC-500 MHz, 92 dB Logarithmic Amplifier PDF資料下載

參數資料

| 型號: | AD8307AR-REEL |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 運動控制電子 |

| 英文描述: | Low Cost DC-500 MHz, 92 dB Logarithmic Amplifier |

| 中文描述: | LOG OR ANTILOG AMPLIFIER, 490 MHz BAND WIDTH, PDSO8 |

| 封裝: | MS-012AA, SOIC-8 |

| 文件頁數: | 11/20頁 |

| 文件大小: | 394K |

| 代理商: | AD8307AR-REEL |

AD8307

–11–

REV. A

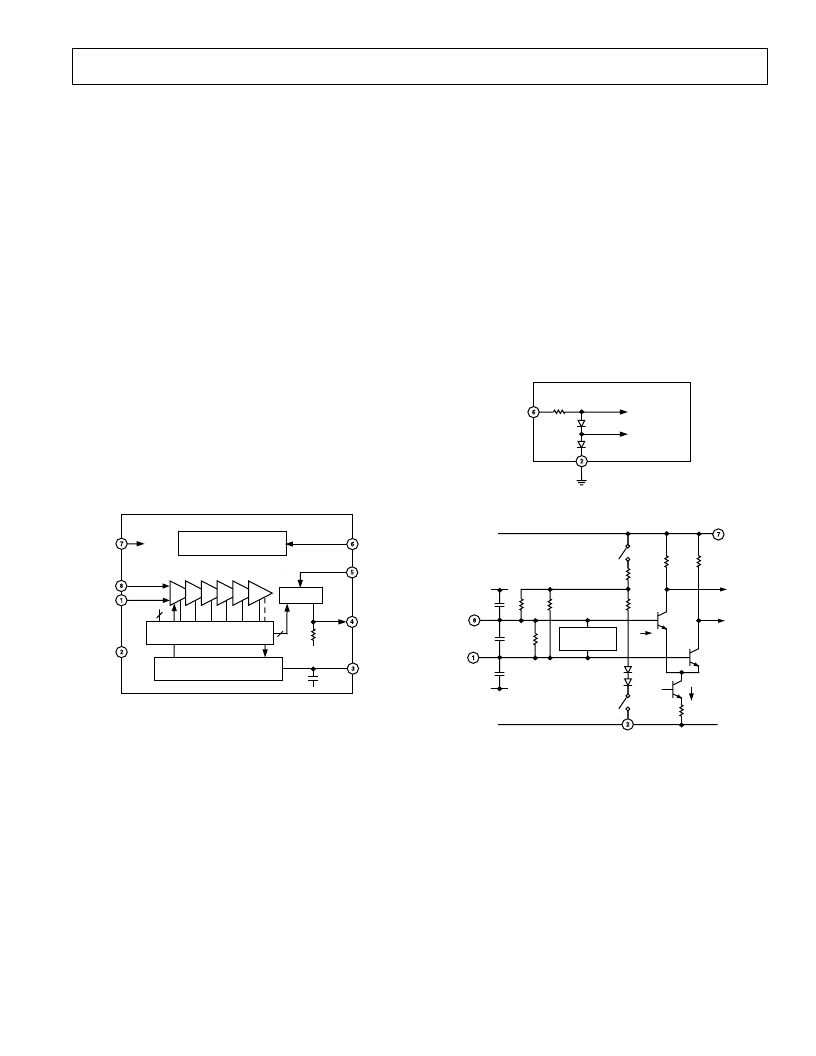

PRODUCT OVE RVIE W

T he AD8307 comprises six main amplifier/limiter stages, each

having a gain of 14.3 dB and small signal bandwidth of 900 MHz;

the overall

gain is 86 dB with a –3 dB bandwidth of 500 MHz.

T hese six cells, and their associated g

m

-styled full-wave detec-

tors, handle the lower two-thirds of the dynamic range. T hree

top-end detectors, placed at 14.3 dB taps on a passive attenua-

tor, handle the upper third of the 90 dB range. Biasing for these

cells is provided by two references: one determines their gain;

the other is a bandgap circuit that determines the logarithmic

slope and stabilizes it against supply- and temperature-variations.

T he AD8307 may be enabled/disabled by a CMOS-compatible

level at ENB (Pin 6). T he first amplifier stage provides a low

voltage noise spectral density (1.5 nV/

√

Hz

).

T he differential current-mode outputs of the nine detectors are

summed and then converted to single-sided form in the output

stage, nominally scaled 2

μ

A/dB. T he logarithmic output voltage

is developed by applying this current to an on-chip 12.5 k

resistor, resulting in a logarithmic slope of 25 mV/dB (i.e.,

500 mV/decade) at OUT . T his voltage is not buffered, allowing

the use of a variety of special output interfaces, including the

addition of post-demodulation filtering. T he last detector stage

includes a modification to temperature-stabilize the log intercept,

which is accurately positioned to make optimal use of the full

output voltage range available. T he intercept may be adjusted

using the pin INT , which adds or subtracts a small current to

the signal current.

BAND GAP REFERENCE

AND BIASING

SIX 14.3dB 900MHz

AMPLIFIER STAGES

MIRROR

INPUT– OFFSET

COMPENSATION LOOP

COMMON

–INPUT

+INPUT

SUPPLY

ENABLE

INT. ADJ

OUTPUT

OFS. ADJ.

AD8307

7.5mA

1.1k

V

3

2

2

m

A

/dB

12.5k

V

COM

NINE DETECTOR CELLS

SPACED 14.3dB

INT

ENB

OUT

OFS

COM

INM

INP

VPS

COM

Figure 25. Main Features of the AD8307

T he last gain stage also includes an offset-sensing cell. T his

generates a bipolarity output current when the main signal path

has an imbalance due to accumulated dc offsets. T his current is

integrated by an on-chip capacitor (which may be increased in

value by an off-chip component, at OFS). T he resulting voltage

is used to null the offset at the output of the first stage. Since it

does not involve the signal input connections, whose ac coupling

capacitors otherwise introduce a second pole in the feedback

path, the stability of the offset correction loop is assured.

T he AD8307 is built

on an advanced dielectrically-isolated

complementary bipolar process.

Most resistors are thin-film

types having a low temperature coefficient of resistance (T CR)

and high linearity under large signal conditions. T heir absolute

tolerance will typically be within

±

20%. Similarly, the capacitors

have a typical tolerance of

±

15% and essentially zero tempera-

ture or voltage sensitivity. Most interfaces have additional small

junction capacitances associated with them, due to active

devices or ESD protection; these may be neither accurate nor

stable. Component numbering in each of these interface dia-

grams is local.

E nable Interface

T he chip-enable interface is shown in Figure 26. T he currents

in the diode-connected transistors control the turn-on and turn-

off states of the bandgap reference and the bias generator, and

are a maximum of 100

μ

A when Pin 6 is taken to 5 V, under

worst case conditions. Left unconnected, or at a voltage below

1 V, the AD8307 will be disabled and consume a sleep current

of under 50

μ

A; tied to the supply, or a voltage above 2 V, it will

be fully enabled. T he internal bias circuitry is very fast (typically

<100 ns for either OFF or ON), and in practice the latency

period before the log amp exhibits its full dynamic range is more

likely to be limited by factors relating to the use of ac coupling

at the input or the settling of the offset-control loop (see follow-

ing sections).

COM

ENB

40k

V

TO BIAS

STAGES

AD8307

Figure 26. Enable Interface

TOP-END

DETECTORS

COM

INP

INM

C

P

C

D

C

M

COM

4k

V

~3k

V

125

V

6k

V

6k

V

2k

V

TYP +2.2V FOR

+3V SUPPLY,

+3.2V AT +5V

S

S

VPS

COM

I

2.4mA

Q1

Q2

Figure 27. Signal Input Interface

Input Interface

Figure 27 shows the essentials of the signal input interface. C

P

and C

M

are the parasitic capacitances to ground; C

D

is the dif-

ferential input capacitance, mostly due to Q1 and Q2. In most

applications both input pins are ac-coupled. T he switches S

close when Enable is asserted. When disabled, the inputs float,

bias current I

E

is shut off, and the coupling capacitors remain

charged. If the log amp is disabled for long periods, small leak-

age currents will discharge these capacitors. If they are poorly

matched, charging currents at power-up can generate a transient

input voltage which may block the lower reaches of the dynamic

range until it has become much less than the signal.

相關PDF資料 |

PDF描述 |

|---|---|

| AD8307 | Low Cost DC-500 MHz, 92 dB Logarithmic Amplifier(對數放大器) |

| AD8309ARU-REEL | 5 MHz.500 MHz 100 dB Demodulating Logarithmic Amplifier with Limiter Output |

| AD8309-EVAL | 5 MHz.500 MHz 100 dB Demodulating Logarithmic Amplifier with Limiter Output |

| AD8309ARU | 5 MHz.500 MHz 100 dB Demodulating Logarithmic Amplifier with Limiter Output |

| AD8309ARU-REEL7 | 5 MHz.500 MHz 100 dB Demodulating Logarithmic Amplifier with Limiter Output |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD8307AR-REEL7 | 功能描述:IC LOGARITHMIC AMP 8-SOIC RoHS:否 類別:集成電路 (IC) >> 線性 - 放大器 - 專用 系列:- 產品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:60 系列:- 類型:可變增益放大器 應用:CATV 安裝類型:表面貼裝 封裝/外殼:20-WQFN 裸露焊盤 供應商設備封裝:20-TQFN-EP(5x5) 包裝:托盤 |

| AD8307ARZ | 功能描述:IC LOGARITHMIC AMP 92DB 8-SOIC RoHS:是 類別:集成電路 (IC) >> 線性 - 放大器 - 專用 系列:- 產品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:60 系列:- 類型:可變增益放大器 應用:CATV 安裝類型:表面貼裝 封裝/外殼:20-WQFN 裸露焊盤 供應商設備封裝:20-TQFN-EP(5x5) 包裝:托盤 |

| AD8307ARZ | 制造商:Analog Devices 功能描述:Logarithmic Amplifier IC |

| AD8307ARZ-REEL | 功能描述:IC AMP LOGARITHMIC 8SOIC RoHS:是 類別:集成電路 (IC) >> 線性 - 放大器 - 專用 系列:- 產品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:60 系列:- 類型:可變增益放大器 應用:CATV 安裝類型:表面貼裝 封裝/外殼:20-WQFN 裸露焊盤 供應商設備封裝:20-TQFN-EP(5x5) 包裝:托盤 |

| AD8307ARZ-RL7 | 功能描述:IC AMP LOGARITHMIC 8-SOIC RoHS:是 類別:集成電路 (IC) >> 線性 - 放大器 - 專用 系列:- 產品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:60 系列:- 類型:可變增益放大器 應用:CATV 安裝類型:表面貼裝 封裝/外殼:20-WQFN 裸露焊盤 供應商設備封裝:20-TQFN-EP(5x5) 包裝:托盤 |

發布緊急采購,3分鐘左右您將得到回復。