- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373959 > AD9101 (Analog Devices, Inc.) 125 MSPS Monolithic Sampling Amplifier(125MSPS單片采樣放大器) PDF資料下載

參數(shù)資料

| 型號: | AD9101 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | 125 MSPS Monolithic Sampling Amplifier(125MSPS單片采樣放大器) |

| 中文描述: | 125 MSPS的采樣單片放大器(125MSPS單片采樣放大器) |

| 文件頁數(shù): | 7/12頁 |

| 文件大小: | 213K |

| 代理商: | AD9101 |

AD9101

–7–

REV. 0

provides a good example. It operates on a single negative supply

with the input range from 0 V to –2 V. By connecting Pins 1

and 2 (RT N) to a +0.33 V level, rather than its usual ground

connection, a bipolar

±

0.25 V input is shifted to 0 V to –2 V at

the AD9101’s output (see Figure 3 in the Applications section.)

APPLIC AT IONS

Because of its rapid acquisition and low distortion, the AD9101

is useful in a wide range of signal processing.

Choosing Between the AD9100 and AD9101

T he first obvious difference between the AD9100 and AD9101

is sample rate. Simplistically, any high resolution system (12–16

bits) operating below 25 MSPS will use the AD9100 and 8–12

bit systems operating above 25 MSPS will use the AD9101.

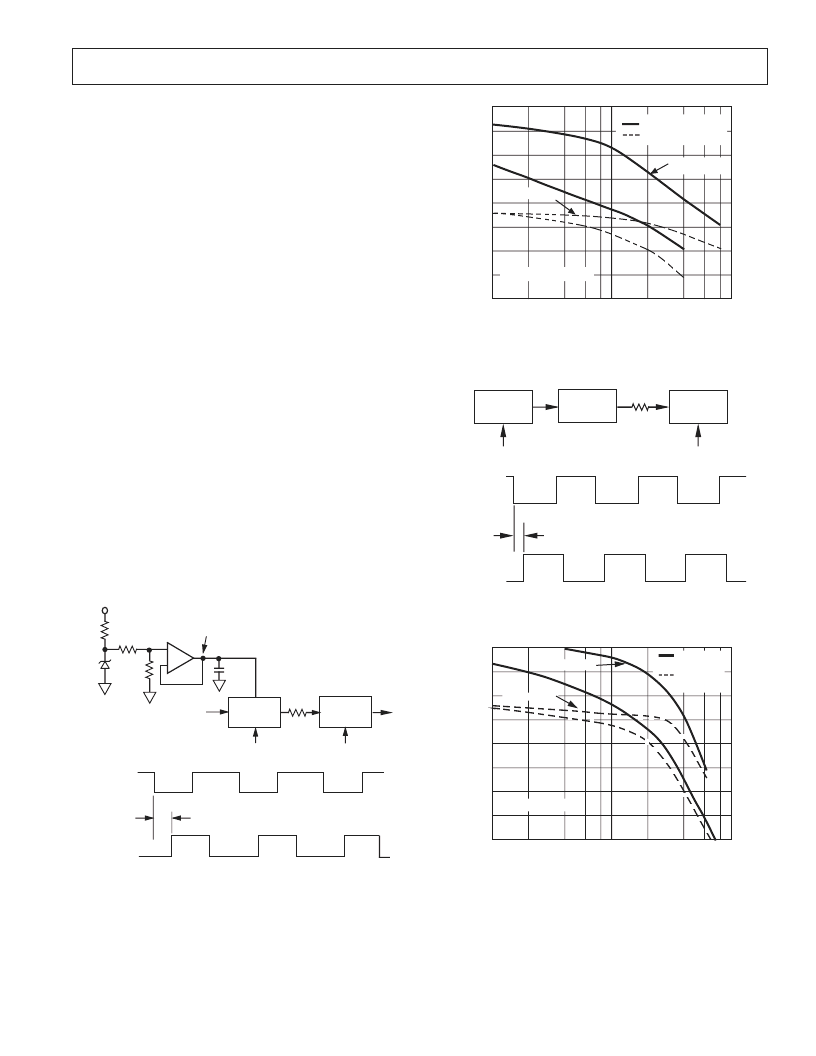

T here are, however, some subtle characteristics of these high

performance track-and-hold amplifiers that create some excep-

tions to these guidelines. T he typical curve entitled “Dynamic

Range vs. Analog Frequency” should be considered when

choosing between these two high performance track-and-holds.

When speed is critical, the AD9101 should receive strong con-

sideration, even in high resolution systems. Using a reduced sig-

nal amplitude through the AD9100 greatly reduces slew limiting

effects and should also be considered when converting high fre-

quency (up to 70 MHz) analog signals with encode rates below

25 MSPS.

Sampler for Flash ADC

Flash ADCs typically suffer degradation of dynamic range as

signal frequency increases. T he AD9101 was designed specifi-

cally for the purpose of boosting this performance and allowing

users to obtain maximum performance with flash ADCs. Figure

3 shows the block diagram and timing relationship for an 8-bit,

125 MSPS converter.

CLOCK 1

CLOCK 2

+

–

1k

3k

1k

0.33V

0.1μF

+5V

AD9002

40

AD9101

AC

RTN

HOLD

3.5 ns

4.5 ns

HOLD

TRACK

HOLD

TRACK

HOLD

3.5 ns

4.5 ns

3.5 ns

CLOCK 2

(AD9002)

TRACK

TRACK

HOLD

TRACK

3.6 ns

4.4 ns

3.6 ns

44 ns

3.6 ns

CLOCK 1

(AD9101)

1.6 ns

Figure 3. AD9101 with 8-Bit, 125 MSPS Flash

Figure 4 contrasts performance of the flash converter alone vs.

the circuit of Figure 3.

Figures 5 and 6 show the block diagrams and dynamic range

improvement when the AD9101 is used ahead of an 10-bit, 75

MSPS flash converter. T he AD9630 is not required if the input

frequency is limited to 40 MHz.

–70

–50

–30

1

10

MHz

100

–45

–40

–35

–55

–60

–65

d

WITH AD9101

ENCODE = 125 MSPS

WORST HARMONIC

SNR W/HARMONICS

A

WITH AD9101

Figure 4. AD9002 Dynamic Range With and Without

AD9101

8 ns

8.5 ns

8 ns

8.5 ns

8.5 ns

"TRACK"

"HOLD"

"TRACK"

"HOLD"

"TRACK"

CLOCK 1

8.25 ns

8.25 ns

8.25 ns

8.25 ns

8.25 ns

"HOLD"

"TRACK"

"HOLD"

"TRACK"

"HOLD"

CLOCK 2

AD9101

AD9630

AD9060

27

CLOCK 1

CLOCK 2

2.5 ns

Figure 5. AD9101 with 10-Bit, 75 MSPS ADC

–70

–50

–30

1

10

MHz

100

–45

–40

–35

–55

–60

–65

WITH AD9101

d

ENCODE = 60 MSPS

WITH AD9101

WORST

HARMONIC

SNR W/

HARMONICS

Figure 6. AD9060 Dynamic Performance With and With-

out AD9101

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD9200KST | Complete 10-Bit, 20 MSPS, 80 mW CMOS A/D Converter |

| AD9200LQFP-EVAL | Complete 10-Bit, 20 MSPS, 80 mW CMOS A/D Converter |

| AD9200JRSRL | Complete 10-Bit, 20 MSPS, 80 mW CMOS A/D Converter |

| AD9200ARSRL | Complete 10-Bit, 20 MSPS, 80 mW CMOS A/D Converter |

| AD9200 | Complete 10-Bit, 20 MSPS, 80 mW CMOS A/D Converter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9101AE | 制造商:AD 制造商全稱:Analog Devices 功能描述:125 MSPS Monolithic Sampling Amplifier |

| AD9101AR | 制造商:Analog Devices 功能描述: |

| AD9101AR-REEL | 制造商:Analog Devices 功能描述:SAMPLE AND HOLD 1CH 0.016US 20SOIC W - Tape and Reel |

| AD9101ARZ | 制造商:Analog Devices 功能描述:- Bulk |

| AD9101SE | 制造商:AD 制造商全稱:Analog Devices 功能描述:125 MSPS Monolithic Sampling Amplifier |

發(fā)布緊急采購,3分鐘左右您將得到回復。