- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373959 > AD9200LQFP-EVAL (Analog Devices, Inc.) Complete 10-Bit, 20 MSPS, 80 mW CMOS A/D Converter PDF資料下載

參數(shù)資料

| 型號: | AD9200LQFP-EVAL |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Complete 10-Bit, 20 MSPS, 80 mW CMOS A/D Converter |

| 中文描述: | 完整的10位,20 MSPS的80毫瓦的CMOS A / D轉(zhuǎn)換 |

| 文件頁數(shù): | 9/24頁 |

| 文件大小: | 338K |

| 代理商: | AD9200LQFP-EVAL |

AD9200

–9–

REV. E

SUMMARY OF MODES

VOLTAGE REFERENCE

1 V Mode

the internal reference may be set to 1 V by connect-

ing REFSENSE and VREF together.

2 V Mode

the internal reference my be set to 2 V by connecting

REFSENSE to analog ground

External Divider Mode

the internal reference may be set to a

point between 1 V and 2 V by adding external resistors. See

Figure 16f.

External Reference Mode

enables the user to apply an exter-

nal reference to REFTS, REFBS and VREF pins. This mode

is attained by tying REFSENSE to VDD.

REFERENCE BUFFER

Center Span Mode

midscale is set by shorting REFTS and

REFBS together and applying the midscale voltage to that point

The MODE pin is set to AVDD/2. The analog input will swing

about that midscale point.

Top/Bottom Mode

sets the input range between two points.

The two points are between 1 V and 2 V apart. The Top/Bottom

Mode is enabled by tying the MODE pin to AVDD.

ANALOG INPUT

Differential Mode

is attained by driving the AIN pin as one

differential input and shorting REFTS and REFBS together and

driving them as the second differential input. The MODE pin

is tied to AVDD/2. Preferred mode for optimal distortion

performance.

Single-Ended

is attained by driving the AIN pin while the

REFTS and REFBS pins are held at dc points. The MODE pin is

tied to AVDD.

Single-Ended/Clamped (AC Coupled)

the input may be

clamped to some dc level by ac coupling the input. This is done

by tying the CLAMPIN to some dc point and applying a pulse

to the CLAMP pin. MODE pin is tied to AVDD.

SPECIAL

AD876 Mode

enables users of the AD876 to drop the AD9200

into their socket. This mode is attained by floating or grounding

the MODE pin.

INPUT AND REFERENCE OVERVIEW

Figure 16, a simplified model of the AD9200, highlights the

relationship between the analog input, AIN, and the reference

voltages, REFTS, REFBS and VREF. Like the voltages applied

to the resistor ladder in a flash A/D converter, REFTS and

REFBS define the maximum and minimum input voltages to

the A/D.

The input stage is normally configured for single-ended opera-

tion, but allows for differential operation by shorting REFTS

and REFBS together to be used as the second input.

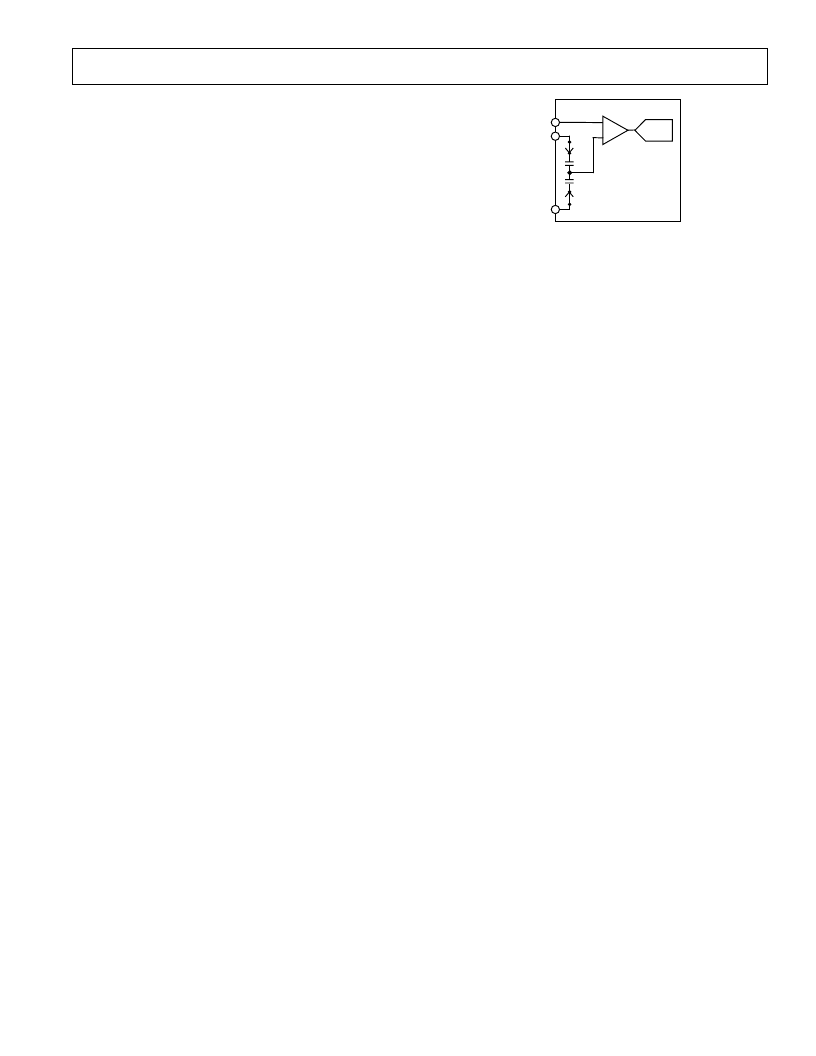

SHA

AIN

REFTS

REFBS

A/D

CORE

AD9200

Figure 15. AD9200 Equivalent Functional Input Circuit

In single-ended operation, the input spans the range,

REFBS

≤

AIN

≤

REFTS

where

REFBS

can be connected to GND and REFTS con-

nected to VREF. If the user requires a different reference range,

REFBS and REFTS can be driven to any voltage within the

power supply rails, so long as the difference between the two is

between 1 V and 2 V.

In differential operation, REFTS and REFBS are shorted to-

gether, and the input span is set by VREF,

(

REFTS

–

VREF/2

)

≤

AIN

≤

(

REFTS

+

VREF/2

)

where

VREF

is determined by the internal reference or brought

in externally by the user.

The best noise performance may be obtained by operating the

AD9200 with a 2 V input range. The best distortion perfor-

mance may be obtained by operating the AD9200 with a 1 V

input range.

REFERENCE OPERATION

The AD9200 can be configured in a variety of reference topolo-

gies. The simplest configuration is to use the AD9200’s onboard

bandgap reference, which provides a pin-strappable option to

generate either a 1 V or 2 V output. If the user desires a refer-

ence voltage other than those two, an external resistor divider

can be connected between VREF, REFSENSE and analog

ground to generate a potential anywhere between 1 V and 2 V.

Another alternative is to use an external reference for designs

requiring enhanced accuracy and/or drift performance. A

third alternative is to bring in top and bottom references,

bypassing VREF altogether.

Figures 16d, 16e and 16f illustrate the reference and input ar-

chitecture of the AD9200. In tailoring a desired arrangement,

the user can select an input configuration to match drive circuit.

Then, moving to the reference modes at the bottom of the

figure, select a reference circuit to accommodate the offset and

amplitude of a full-scale signal.

Table I outlines pin configurations to match user requirements.

相關PDF資料 |

PDF描述 |

|---|---|

| AD9200JRSRL | Complete 10-Bit, 20 MSPS, 80 mW CMOS A/D Converter |

| AD9200ARSRL | Complete 10-Bit, 20 MSPS, 80 mW CMOS A/D Converter |

| AD9200 | Complete 10-Bit, 20 MSPS, 80 mW CMOS A/D Converter |

| AD9200ARS | CAP 33 UF 16V 10% |

| AD9200JRS | Complete 10-Bit, 20 MSPS, 80 mW CMOS A/D Converter |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| AD9200SSOP-EVAL | 制造商:Analog Devices 功能描述:Evaluation Board For AD9200 CMOS A/D Converter 制造商:Analog Devices 功能描述:EVAL BD FOR AD9200 CMOS A/D CNVRTR - Bulk |

| AD9200TQFP-EVAL | 制造商:Analog Devices 功能描述:EVAL BD FOR AD9200 CMOS A/D CNVRTR - Bulk |

| AD9201 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Dual Channel, 20 MHz 10-Bit Resolution CMOS ADC |

| AD9201ARS | 功能描述:IC ADC CMOS 10BIT DUAL 28-SSOP RoHS:否 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 模數(shù)轉(zhuǎn)換器 系列:- 標準包裝:1,000 系列:- 位數(shù):12 采樣率(每秒):300k 數(shù)據(jù)接口:并聯(lián) 轉(zhuǎn)換器數(shù)目:1 功率耗散(最大):75mW 電壓電源:單電源 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:24-SOIC(0.295",7.50mm 寬) 供應商設備封裝:24-SOIC 包裝:帶卷 (TR) 輸入數(shù)目和類型:1 個單端,單極;1 個單端,雙極 |

| AD9201ARSRL | 功能描述:IC ADC 10BIT 2CH 40MSPS 28-SSOP RoHS:否 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 模數(shù)轉(zhuǎn)換器 系列:- 標準包裝:1,000 系列:- 位數(shù):16 采樣率(每秒):45k 數(shù)據(jù)接口:串行 轉(zhuǎn)換器數(shù)目:2 功率耗散(最大):315mW 電壓電源:模擬和數(shù)字 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:28-SOIC(0.295",7.50mm 寬) 供應商設備封裝:28-SOIC W 包裝:帶卷 (TR) 輸入數(shù)目和類型:2 個單端,單極 |

發(fā)布緊急采購,3分鐘左右您將得到回復。