- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373962 > AD9289BBC-65EB (Analog Devices, Inc.) Quad 8-Bit, 65 MSPS Serial LVDS 3V A/D Converter PDF資料下載

參數(shù)資料

| 型號(hào): | AD9289BBC-65EB |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Quad 8-Bit, 65 MSPS Serial LVDS 3V A/D Converter |

| 中文描述: | 四8位,65 MSPS的串行LVDS 3V的A / D轉(zhuǎn)換 |

| 文件頁數(shù): | 4/16頁 |

| 文件大小: | 1376K |

| 代理商: | AD9289BBC-65EB |

AD9289 Prelimnary Technical Data

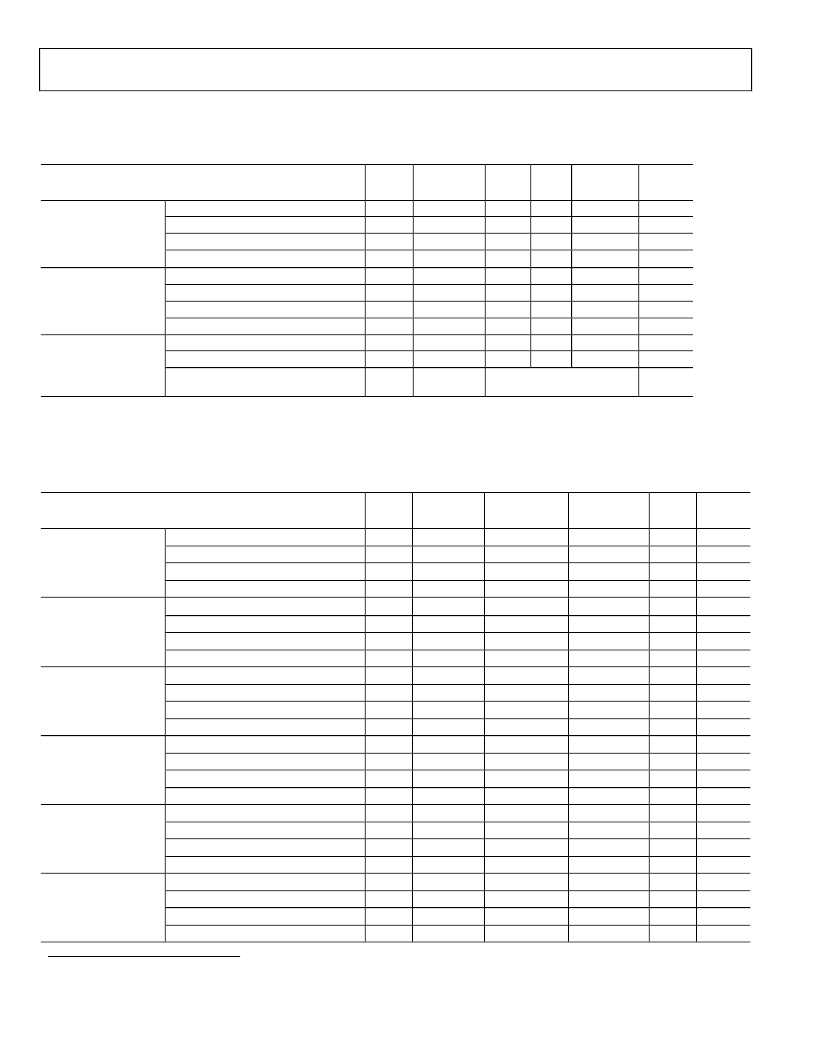

DIGITAL SPECIFICATIONS

Rev. PrJ | Page 4 of 16

6/25/2004

AVDD = 3.0V, DRVDD = 3.0V

Parameter

Temp

Test

Level

Min

Typ

Max

Unit

Differential Input Voltage

1

Input Common Mode Voltage

Input Resistance

Input Capacitance

Logic ‘1’ Voltage

Logic ‘0’ Voltage

Input Resistance

Input Capacitance

Differential Output Voltage (V

OD

)

Output Offset Voltage (V

OS

)

Output Coding

Full

Full

Full

25

°

C

Full

Full

Full

Full

Full

Full

Full

IV

IV

IV

IV

IV

IV

IV

IV

IV

IV

IV

247

2.0

247

1.125

Twos Complement or

Binary

mVpp

V

k

pF

V

V

k

PF

mV

V

1.25

30

4

CLOCK INPUTS

(CLK+, CLK-)

0.8

454

1.375

LOGIC INPUTS

DIGITAL OUTPUTS

(LVDS Mode)

Table 2: Digital Specifications

AC SPECIFICATIONS

2

AVDD = 3.0 V, DRVDD = 3.0 V; INTERNAL REF; DIFFERENTIAL ANALOG AND CLOCK INPUT, LVDS OUTPUT

MODE

Parameter

Temp

Test

Level

Min

Typ

Max

Unit

f

IN

= 10.3 MHz

f

IN

= 19.6 MHz

f

IN

= 32.5 MHz

f

IN

= 51 MHz

f

IN

= 10.3 MHz

f

IN

= 19.6 MHz

f

IN

= 32.5 MHz

f

IN

= 51 MHz

f

IN

= 10.3 MHz

f

IN

= 19.6 MHz

f

IN

= 32.5 MHz

f

IN

= 51 MHz

f

IN

= 10.3 MHz

f

IN

= 19.6 MHz

f

IN

= 32.5 MHz

f

IN

= 51 MHz

f

IN

= 10.3 MHz

f

IN

= 19.6 MHz

f

IN

= 32.5 MHz

f

IN

= 51 MHz

f

IN

= 10.3 MHz

f

IN

= 19.6 MHz

f

IN

= 32.5 MHz

f

IN

= 51 MHz

25

°

C

25

°

C

25

°

C

25

°

C

25

°

C

25

°

C

25

°

C

25

°

C

25

°

C

25

°

C

25

°

C

25

°

C

25

°

C

25

°

C

25

°

C

25

°

C

25

°

C

25

°

C

25

°

C

25

°

C

25

°

C

25

°

C

25

°

C

25

°

C

V

V

I

V

V

V

I

V

V

V

I

V

V

V

I

V

V

V

I

V

V

V

I

V

47.5

47.5

47

47

7.5

7.5

62

59

62

59

60

58

dB

dB

dB

dB

dB

dB

dB

dB

Bits

Bits

Bits

Bits

dB

dB

dB

dB

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

SIGNAL TO NOISE

RATIO (SNR) –

Without Harmonics

SIGNAL TO NOISE

RATIO (SINAD) –

With Harmonics

EFFECTIVE

NUMBER OF BITS

(ENOB)

SPURIOUS FREE

DYNAMIC RANGE

(SFDR)

SECOND AND

THIRD HARMONIC

DISTORTION

TOTAL HARMONIC

DISTORTION (THD)

1

Clock Inputs are LVDS compatible .Clock Inputs require external DC bias and cannot be AC coupled.

2

SNR/harmonics based on an analog input voltage of –0.5 dBFS referenced to a 1 Vpp full-scale input range.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD9300 | 4 x 1 Wideband Video Multiplexer |

| AD9300KP | 4 x 1 Wideband Video Multiplexer |

| AD9300KQ | 4 x 1 Wideband Video Multiplexer |

| AD9410 | 10-Bit, 210 MSPS A/D Converter |

| AD9410BSQ | 10-Bit, 210 MSPS A/D Converter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9289BBCZ | 制造商:Analog Devices 功能描述:ADC Quad Pipelined 65Msps 8-bit Serial 64-Pin CSP-BGA |

| AD9300 | 制造商:AD 制造商全稱:Analog Devices 功能描述:4 x 1 Wideband Video Multiplexer |

| AD9300KP | 制造商:Analog Devices 功能描述: 制造商:Analog Devices 功能描述:4-CHANNEL, VIDEO MULTIPLEXER, PQCC20 |

| AD9300KP-REEL | 制造商:Analog Devices 功能描述: |

| AD9300KQ | 制造商:AD 制造商全稱:Analog Devices 功能描述:4 x 1 Wideband Video Multiplexer |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。