- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373975 > ADAU1401 (Analog Devices, Inc.) SigmaDSP 28-/56-Bit Audio Processor with Two ADCs and Four DACs PDF資料下載

參數(shù)資料

| 型號: | ADAU1401 |

| 廠商: | Analog Devices, Inc. |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | SigmaDSP 28-/56-Bit Audio Processor with Two ADCs and Four DACs |

| 中文描述: | SigmaDSP的28-/56-Bit音頻處理器雙ADC和4個DAC |

| 文件頁數(shù): | 16/52頁 |

| 文件大小: | 785K |

| 代理商: | ADAU1401 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

ADAU1401

INITIALIZATION

This section details the procedure for properly setting up the

ADAU1401. The following five-step sequence provides an

overview of how to initialize the IC:

1.

Apply power to ADAU1401.

2.

Wait for PLL to lock.

3.

Load SigmaDSP program and parameters.

4.

Set up registers (including multipurpose pins and digital

interfaces).

5.

Turn off the default muting of the converters, clear the

data registers, and initialize the DAC setup register (see

the Control Registers Setup section for specific settings).

Rev. 0 | Page 16 of 52

Table 12 lists typical times to boot the ADAU1401 into an

application’s operational state, assuming a 400 kHz I

2

C clock

loading a full program, parameter set, and all registers (about

8.5 kB). In reality, most applications will not fill the RAMs and

therefore boot time (Column 3 of

CONTROL REGISTERS SETUP

The following registers must be set as described in this section

to initialize the ADAU1401. These settings are the basic

minimum settings needed to operate the IC with an analog

input/output of 48 kHz. More registers may need to be set,

depending on the application. See the

section for additional settings.

DSP Core Control Register (Address 2076)

Set Bits [4:2] (ADM, DAM, and CR) each to 1.

DAC Setup Register (Address 2087)

Set Bits [0:1] (DS [1:0]) to 01.

RECOMMENDED PROGRAM/PARAMETER

LOADING PROCEDURE

When writing large amounts of data to the program or parameter

RAM in direct write mode, the processor core should be disabled

to prevent unpleasant noises from appearing in the audio output.

1.

Set Bit 3 and Bit 4 (active low) of the core control register

to 1 to mute the ADCs and DACs. This begins a volume

ramp-down.

2.

Set Bit 2 (active low) of the core control register to 1. This

zeroes the SigmaDSP accumulators, the data output registers,

and the data input registers.

3.

Fill the program RAM using burst mode writes.

4.

Fill the parameter RAM using burst mode writes.

5.

Deassert Bit 2 to Bit 4 of the core control register.

Table 12) will be less.

RAMs and Registers

To only test analog audio pass-through (ADCs to DACs), Steps 3

and 4 can be skipped and the default internal program can be used.

POWER-UP SEQUENCE

The ADAU1401 has a built-in power-up sequence that

initializes the contents of all internal RAMs on power-up or

when the device is brought out of a reset. On the positive edge

of

RESET, the contents of the internal program boot ROM are

copied to the internal program RAM memory, the parameter

RAM is filled with values (all 0s) from its associated boot ROM,

and all registers are initialized to 0s. The default boot ROM

program copies audio from the inputs to the outputs without

processing it (see

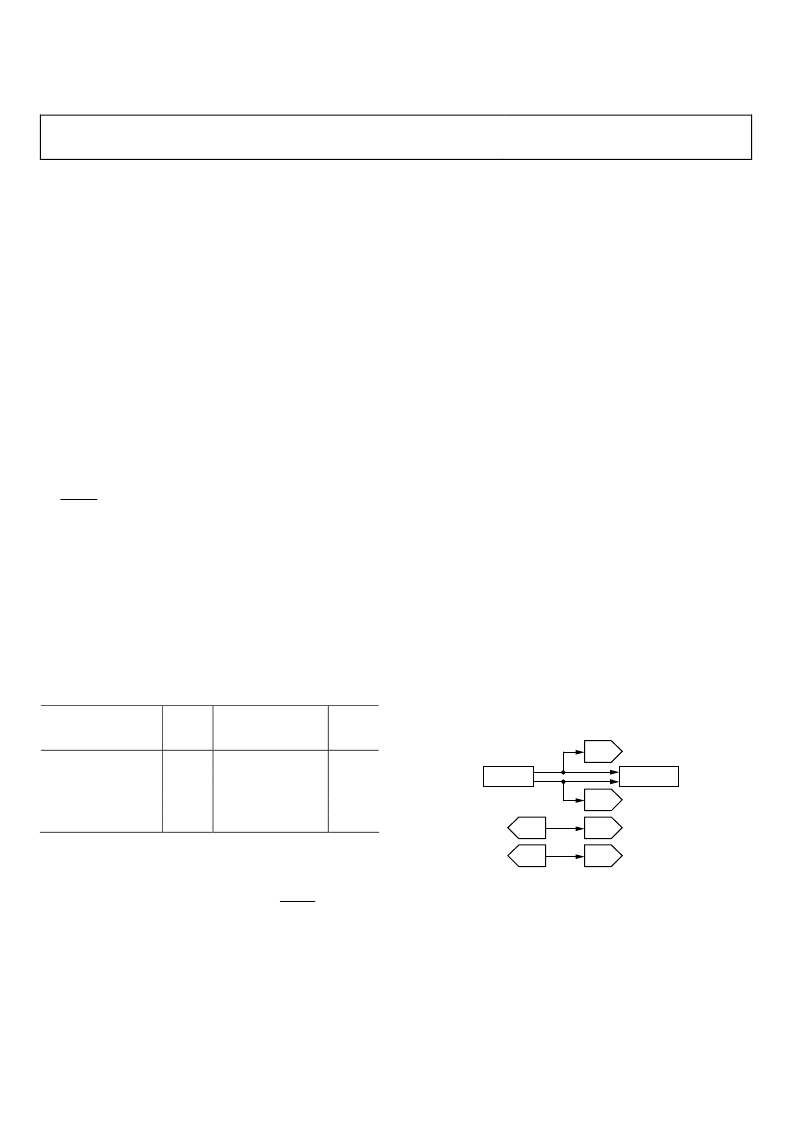

Figure 13). In this program, serial digital

Input 0 and Input 1 are output on DAC0 and DAC1 and serial

digital Output 0 and Output 1. ADC0 and ADC1 are output on

DAC2 and DAC3. The data memories are also zeroed at power-

up. New values should not be written to the control port until

the initialization is complete.

Table 12. Power-Up Time

Max Program/

Parameter/Register

Boot Time (I

2

C)

175 ms

175 ms

175 ms

175 ms

175 ms

MCLKI Input

3.072 MHz (64 × f

S

)

11.289 MHz (256 × f

S

)

12.288 MHz (256 × f

S

)

18.432 MHz (384 × f

S

)

24.576 MHz (512 × f

S

)

The PLL start-up time lasts for 2

18

cycles of the clock on the

MCLKI pin. This time ranges from 10.7 ms for a 24.576 MHz

(512 × f

S

) input clock to 85.3 ms for a 3.072 MHz (64 × f

S

) input

clock and is measured from the rising edge of

the PLL startup, the duration of the ADAU1401 boot cycle is about

42 μs for a f

S

of 48 kHz. The user should avoid writing to or reading

from the ADAU1401 during this start-up time. For an MCLK input

of 12.288 MHz, the full initialization sequence (PLL startup plus

boot cycle) is approximately 21 ms. As the device comes out of a

reset, the clock mode is immediately set by the PLL_MODE0 and

PLL_MODE1 pins. The reset is synchronized to the falling edge

of the internal clock.

Init.

Time

85 ms

23 ms

21 ms

16 ms

11 ms

Total

260 ms

198 ms

196 ms

191 ms

186 ms

ADC0

DAC1

DAC0

DAC2

DAC3

ADC1

SDATA_IN0

SDATA_OUT0

0

Figure 13. Default Program Signal Flow

POWER-REDUCTION MODES

Sections of the ADAU1401 chip can be turned on and off as

needed to reduce power consumption. These include the ADCs,

DACs, and voltage reference.

The individual analog sections can be turned off by writing to

the auxiliary ADC and power control register. By default, the

ADCs, DACs, and reference are enabled (all bits set to 0). Each

of these can be turned off by writing a 1 to the appropriate bits

in this register. The ADC power-down mode powers down both

RESET. Following

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADAU1401YSTZ | SigmaDSP 28-/56-Bit Audio Processor with Two ADCs and Four DACs |

| ADAU1401YSTZ-RL | SigmaDSP 28-/56-Bit Audio Processor with Two ADCs and Four DACs |

| ADAU1513 | Class-D Audio Power Stage |

| ADAU1513ACPZ | Class-D Audio Power Stage |

| ADAU1513ACPZ-RL | Class-D Audio Power Stage |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADAU1401A | 制造商:AD 制造商全稱:Analog Devices 功能描述:SigmaDSP 28-/56-Bit Audio Processor with Two ADCs and Four DACs |

| ADAU1401AWBSTZ | 功能描述:IC AUDIO PROC 28/56BIT 48LQFP RoHS:是 類別:集成電路 (IC) >> 線性 - 音頻處理 系列:SigmaDSP® 其它有關(guān)文件:STA321 View All Specifications 標準包裝:1 系列:Sound Terminal™ 類型:音頻處理器 應用:數(shù)字音頻 安裝類型:表面貼裝 封裝/外殼:64-LQFP 裸露焊盤 供應商設備封裝:64-LQFP EP(10x10) 包裝:Digi-Reel® 其它名稱:497-11050-6 |

| ADAU1401AWBSTZ-RL | 功能描述:IC AUDIO PROC 28/56BIT 48LQFP RoHS:是 類別:集成電路 (IC) >> 線性 - 音頻處理 系列:SigmaDSP® 其它有關(guān)文件:STA321 View All Specifications 標準包裝:1 系列:Sound Terminal™ 類型:音頻處理器 應用:數(shù)字音頻 安裝類型:表面貼裝 封裝/外殼:64-LQFP 裸露焊盤 供應商設備封裝:64-LQFP EP(10x10) 包裝:Digi-Reel® 其它名稱:497-11050-6 |

| ADAU1401YSTZ | 功能描述:IC AUDIO PROC 28/56BIT 48LQFP RoHS:是 類別:集成電路 (IC) >> 線性 - 音頻處理 系列:SigmaDSP® 其它有關(guān)文件:STA321 View All Specifications 標準包裝:1 系列:Sound Terminal™ 類型:音頻處理器 應用:數(shù)字音頻 安裝類型:表面貼裝 封裝/外殼:64-LQFP 裸露焊盤 供應商設備封裝:64-LQFP EP(10x10) 包裝:Digi-Reel® 其它名稱:497-11050-6 |

| ADAU1401YSTZ-RL | 功能描述:IC AUDIO PROC 28/56BIT 48LQFP RoHS:是 類別:集成電路 (IC) >> 線性 - 音頻處理 系列:SigmaDSP® 其它有關(guān)文件:STA321 View All Specifications 標準包裝:1 系列:Sound Terminal™ 類型:音頻處理器 應用:數(shù)字音頻 安裝類型:表面貼裝 封裝/外殼:64-LQFP 裸露焊盤 供應商設備封裝:64-LQFP EP(10x10) 包裝:Digi-Reel® 其它名稱:497-11050-6 |

發(fā)布緊急采購,3分鐘左右您將得到回復。