- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄373975 > ADAU1401YSTZ (ANALOG DEVICES INC) SigmaDSP 28-/56-Bit Audio Processor with Two ADCs and Four DACs PDF資料下載

參數(shù)資料

| 型號(hào): | ADAU1401YSTZ |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | SigmaDSP 28-/56-Bit Audio Processor with Two ADCs and Four DACs |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| 封裝: | ROHS COMPLIANT, PLASTIC, MS-026BBC, LQFP-48 |

| 文件頁(yè)數(shù): | 6/52頁(yè) |

| 文件大小: | 785K |

| 代理商: | ADAU1401YSTZ |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)當(dāng)前第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)

ADAU1401

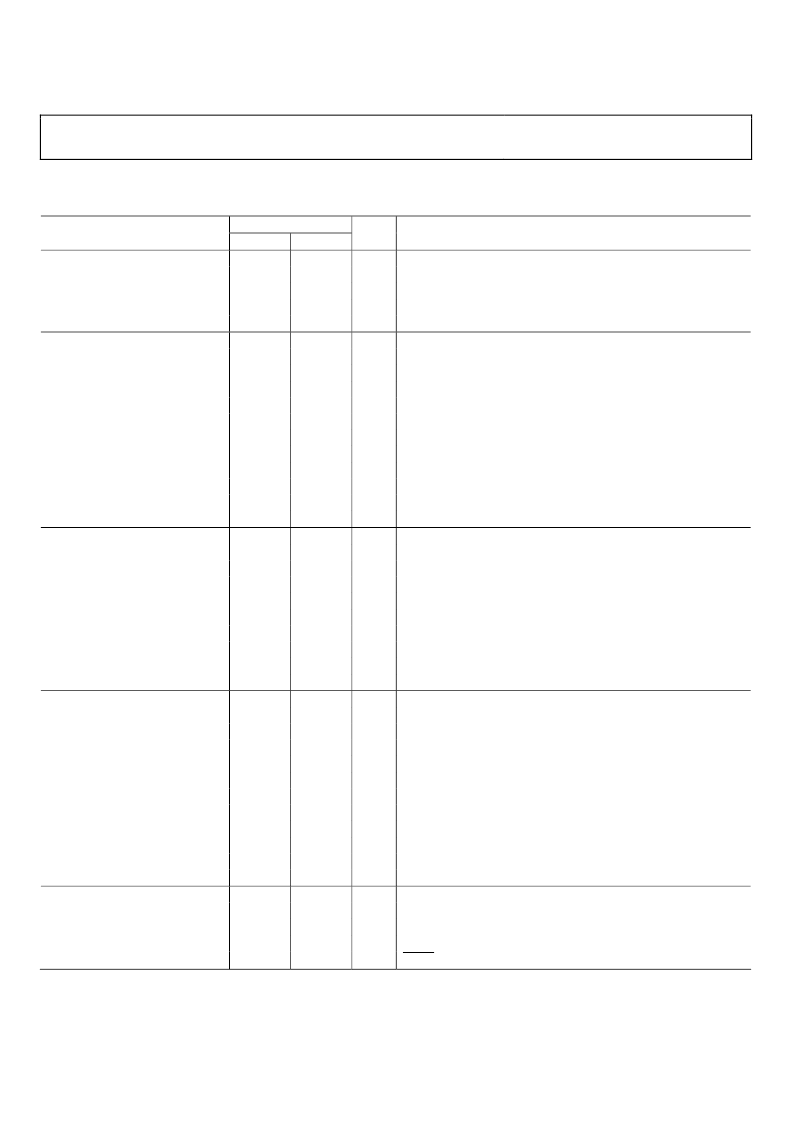

DIGITAL TIMING SPECIFICATIONS

Rev. 0 | Page 6 of 52

Table 8. Digital Timing

1

Parameter

MASTER CLOCK

t

MP

t

MP

t

MP

t

MP

SERIAL PORT

t

BIL

t

BIH

t

LIS

t

LIH

t

SIS

t

SIH

t

LOS

t

LOH

t

TS

t

SODS

t

SODM

SPI PORT

f

CCLK

t

CCPL

t

CCPH

t

CLS

t

CLH

t

CLPH

t

CDS

t

CDH

t

COD

I

2

C PORT

f

SCL

t

SCLH

t

SCLL

t

SCS

t

SCH

t

DS

t

SCR

t

SCF

t

SDR

t

SDF

t

BFT

MULTIPURPOSE PINS AND RESET

t

GRT

t

GFT

t

GIL

t

RLPW

1

All timing specifications are given for the default (I

2

S) states of the serial input port and the serial output port (see Table 67).

Limit

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

MHz

ns

ns

ns

ns

ns

ns

ns

ns

kHz

μs

μs

μs

μs

ns

ns

ns

ns

ns

ns

ns

μs

ns

Description

MCLKI period, 512 × f

S

mode.

MCLKI period, 384 × f

S

mode.

MCLKI period, 256 × f

S

mode.

MCLKI period, 64 × f

S

mode.

INPUT_BCLK low pulse width.

INPUT_BCLK high pulse width.

INPUT_LRCLK setup. Time to INPUT_BCLK rising.

INPUT_LRCLK hold. Time from INPUT_BCLK rising.

SDATA_INx setup. Time to INPUT_BCLK rising.

SDATA_INx hold. Time from INPUT_BCLK rising.

OUTPUT_LRCLK setup in slave mode.

OUTPUT_LRCLK hold in slave mode.

OUTPUT_BCLK falling to OUTPUT_LRCLK timing skew.

SDATA_OUTx delay in slave mode. Time from OUTPUT_BCLK falling.

SDATA_OUTx delay in master mode. Time from OUTPUT_BCLK falling.

CCLK frequency.

CCLK pulse width low.

CCLK pulse width high.

CLATCH setup. Time to CCLK rising.

CLATCH hold. Time from CCLK rising.

CLATCH pulse width high.

CDATA setup. Time to CCLK rising.

CDATA hold. Time from CCLK rising.

COUT delay. Time from CCLK falling.

SCL frequency.

SCL high.

SCL low.

Setup time, relevant for repeated start condition.

Hold time. After this period, the first clock is generated.

Data setup time.

SCL rise time.

SCL fall time.

SDA rise time.

SDA fall time.

Bus-free time. Time between stop and start.

GPIO rise time.

GPIO fall time.

GPIO input latency. Time until high/low value is read by core.

RESET low pulse width.

t

MIN

36

48

73

291

40

40

10

10

10

10

10

10

80

80

0

100

80

0

80

0.6

1.3

0.6

0.6

100

0.6

20

t

MAX

244

366

488

1953

5

40

40

6.25

101

400

300

300

300

300

50

50

1.5 × 1/f

S

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADAU1401YSTZ-RL | SigmaDSP 28-/56-Bit Audio Processor with Two ADCs and Four DACs |

| ADAU1513 | Class-D Audio Power Stage |

| ADAU1513ACPZ | Class-D Audio Power Stage |

| ADAU1513ACPZ-RL | Class-D Audio Power Stage |

| ADAU1513ACPZ-RL7 | Class-D Audio Power Stage |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADAU1401YSTZ-RL | 功能描述:IC AUDIO PROC 28/56BIT 48LQFP RoHS:是 類別:集成電路 (IC) >> 線性 - 音頻處理 系列:SigmaDSP® 其它有關(guān)文件:STA321 View All Specifications 標(biāo)準(zhǔn)包裝:1 系列:Sound Terminal™ 類型:音頻處理器 應(yīng)用:數(shù)字音頻 安裝類型:表面貼裝 封裝/外殼:64-LQFP 裸露焊盤(pán) 供應(yīng)商設(shè)備封裝:64-LQFP EP(10x10) 包裝:Digi-Reel® 其它名稱:497-11050-6 |

| ADAU1421YSTZ | 制造商:Analog Devices 功能描述: |

| ADAU1421YSTZ-REEL | 制造商:Analog Devices 功能描述: |

| ADAU1442 | 制造商:AD 制造商全稱:Analog Devices 功能描述:SigmaDSP Digital Audio Processor |

| ADAU1442YSVZ-3A | 功能描述:IC SIGMADSP 28B 175MHZ 100TQFP RoHS:是 類別:集成電路 (IC) >> 線性 - 音頻處理 系列:SigmaDSP® 其它有關(guān)文件:STA321 View All Specifications 標(biāo)準(zhǔn)包裝:1 系列:Sound Terminal™ 類型:音頻處理器 應(yīng)用:數(shù)字音頻 安裝類型:表面貼裝 封裝/外殼:64-LQFP 裸露焊盤(pán) 供應(yīng)商設(shè)備封裝:64-LQFP EP(10x10) 包裝:Digi-Reel® 其它名稱:497-11050-6 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。