- 您現在的位置:買賣IC網 > PDF目錄373975 > ADAU1702JSTZ (ANALOG DEVICES INC) SigmaDSP 28-56-Bit Audio Processor with Two ADCs and Four DACs PDF資料下載

參數資料

| 型號: | ADAU1702JSTZ |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 消費家電 |

| 英文描述: | SigmaDSP 28-56-Bit Audio Processor with Two ADCs and Four DACs |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| 封裝: | ROHS COMPLIANT, PLASTIC, MS-026BBC, LQFP-48 |

| 文件頁數: | 17/52頁 |

| 文件大小: | 773K |

| 代理商: | ADAU1702JSTZ |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

ADAU1702

of these can be turned off by writing a 1 to the appropriate bits

in this register. The ADC power-down mode powers down both

ADCs, and each DAC can be powered down individually. The

current savings is about 15 mA when the ADCs are powered

down and about 4 mA for each DAC that is powered down. The

voltage reference, which is supplied to both the ADCs and

DACs, should only be powered down if all ADCs and DACs are

powered down. The reference is powered down by setting both

Bit 6 and Bit 7 of the control register.

USING THE OSCILLATOR

The ADAU1702 can use an on-board oscillator to generate its

master clock. The oscillator is designed to work with a 256 × f

S

master clock, which is 12.288 MHz for a f

S

of 48 kHz and

11.2896 MHz for a f

S

of 44.1 kHz. The crystal in the oscillator

circuit should be an AT-cut, parallel resonator operating at its

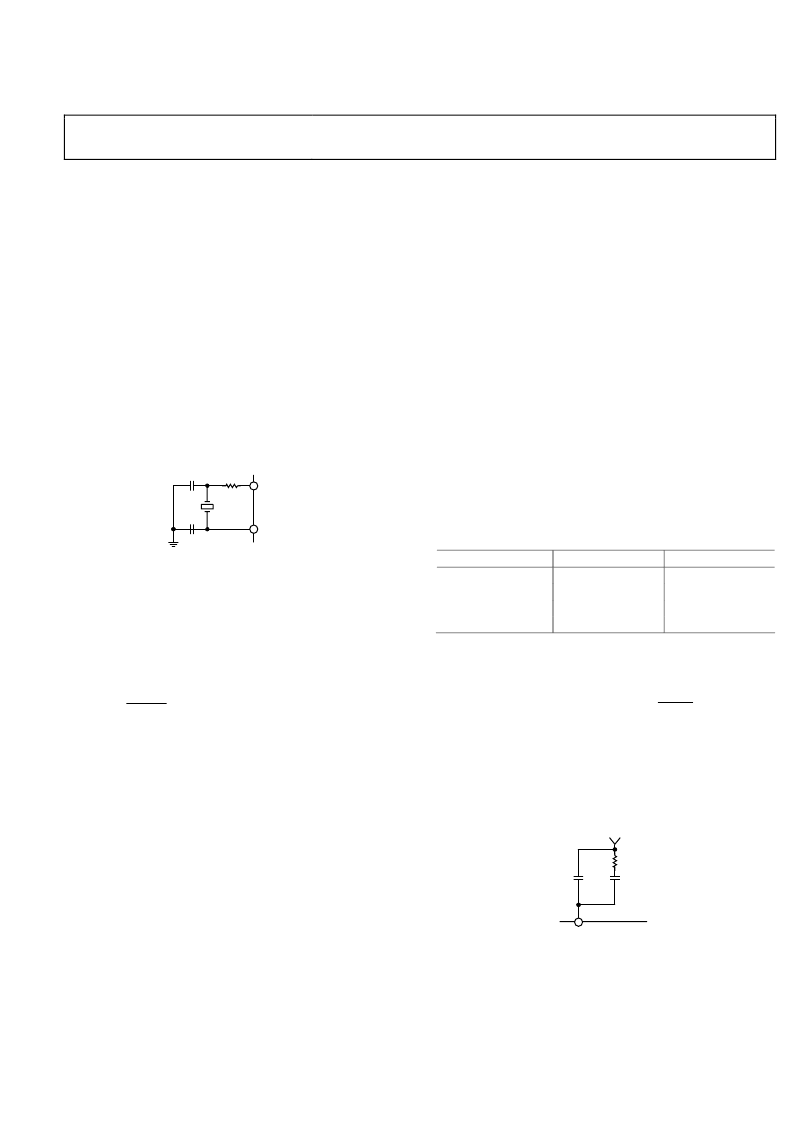

fundamental frequency. Figure 14 shows the external circuit

recommended for proper operation.

ADAU1702

Rev. 0 | Page 17 of 52

C1

100

MCLKI

OSCO

C2

0

Figure 14. Crystal Oscillator Circuit

The 100 Ω damping resistor on OSCO gives the oscillator a

voltage swing of approximately 2.2 V. The crystal shunt capaci-

tance should be 7 pF. Its load capacitance should be about 18 pF,

although the circuit supports values of up to 25 pF. The necessary

values of the C1 and C2 load capacitors can be calculated from

the crystal load capacitance as follows:

C2

C1

C

+

+

where

C

stray

is the stray capacitance in the circuit and is usually

assumed to be approximately 2 pF to 5 pF.

OSCO should not be used to directly drive the crystal signal to

another IC. This signal is an analog sine wave and is not

appropriate to drive a digital input. There are two options for

using the ADAU1702 to provide a master clock to other ICs in

the system. The first, and less recommended method, is to use a

high impedance input digital buffer on the OSCO signal. If this

is done, minimize the trace length to the buffer input. The

second method is to use a clock from the serial output port.

Pin MP11 can be set as an output (master) clock divided down

from the internal core clock. If this pin is set to serial output

port (OUTPUT_BCLK) mode in the multipurpose pin

configuration register (2081) and the port is set to master in

the serial output control register (2078), the desired output

frequency can also be set in the serial output control register

with Bits OBF [1:0] (see Table 49).

stray

L

C

C2

C1

×

=

If the oscillator is not utilized in the design, it can be powered

down to save power. This can be done if a system master clock

is already available in the system. By default, the oscillator is

powered on. The oscillator powers down when a 1 is written to

the OPD bit of the oscillator power-down register (see Table 60).

SETTING MASTER CLOCK/PLL MODE

The MCLK input of the ADAU1702 feeds a PLL, which generates

the 25 MIPS SigmaDSP core clock. In normal operation, the

input to MCLK must be one of the following: 64 × f

S

, 256 × f

S

,

384 × f

S

, or 512 × f

S

, where f

S

is the input sampling rate. The

mode is set on PLL_MODE0 and PLL_MODE1 as described in

Table 12. If the ADAU1702 is set to receive double-rate signals

(by reducing the number of program steps per sample by a factor

of 2 using the core control register), the master clock frequencies

must be 32 × f

S

, 128 × f

S

, 192 × f

S

, or 256 × f

S

. If the ADAU1702

is set to receive quad-rate signals (by reducing the number of

program steps per sample by a factor of 4 using the core control

register), the master clock frequencies must be 16 × f

S

, 64 × f

S

,

96 × f

S

, or 128 × f

S

. On power-up, a clock signal must be present

on MCLK so that the ADAU1702 can complete its initialization

routine.

Table 12. PLL Modes

MCLKI Input

64 × f

S

256 × f

S

384 × f

S

512 × f

S

The clock mode should not be changed without also resetting

the ADAU1702. If the mode is changed during operation, a

click or pop can result in the output signals. The state of the

PLL_MODEx pins should be changed while RESET is held low.

PLL_MODE0

0

0

1

1

PLL_MODE1

0

1

0

1

The PLL loop filter should be connected to the PLL_LF pin. This

filter, shown in Figure 15, includes three passive components—

two capacitors and a resistor. The values of these components

do not need to be exact; the tolerance can be up to 10% for the

resistor and up to 20% for the capacitors. The 3.3 V signal shown in

Figure 15 can be connected to the AVDD supply of the chip.

ADAU1702

3.3V

475

PLL_LF

56nF

3.3nF

0

Figure 15. PLL Loop Filter

相關PDF資料 |

PDF描述 |

|---|---|

| ADAU1702JSTZ-RL | SigmaDSP 28-56-Bit Audio Processor with Two ADCs and Four DACs |

| ADC912A | CMOS Microprocessor-Compatible 12-Bit A/D Converter |

| ADC912AFP | CMOS Microprocessor-Compatible 12-Bit A/D Converter |

| ADC912AFS | CMOS Microprocessor-Compatible 12-Bit A/D Converter |

| ADCMP341 | Dual 0.275% Comparators and Reference with Programmable Hysteresis |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADAU1702JSTZ-RL | 功能描述:IC AUDIO PROC 2ADC/4DAC 48-LQFP RoHS:是 類別:集成電路 (IC) >> 線性 - 音頻處理 系列:SigmaDSP® 其它有關文件:STA321 View All Specifications 標準包裝:1 系列:Sound Terminal™ 類型:音頻處理器 應用:數字音頻 安裝類型:表面貼裝 封裝/外殼:64-LQFP 裸露焊盤 供應商設備封裝:64-LQFP EP(10x10) 包裝:Digi-Reel® 其它名稱:497-11050-6 |

| ADAU1761 | 制造商:AD 制造商全稱:Analog Devices 功能描述:SigmaDSP Stereo, Low Power, 96 kHz, 24-Bit Audio Codec with Integrated PLL |

| ADAU1761BCPZ | 功能描述:IC SIGMADSP CODEC PLL 32LFCSP RoHS:是 類別:集成電路 (IC) >> 接口 - 編解碼器 系列:SigmaDSP® 標準包裝:2,500 系列:- 類型:PCM 數據接口:PCM 音頻接口 分辨率(位):15 b ADC / DAC 數量:1 / 1 三角積分調變:是 S/N 比,標準 ADC / DAC (db):- 動態范圍,標準 ADC / DAC (db):- 電壓 - 電源,模擬:2.7 V ~ 3.3 V 電壓 - 電源,數字:2.7 V ~ 3.3 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:80-VFBGA 供應商設備封裝:80-BGA MICROSTAR JUNIOR(5x5) 包裝:帶卷 (TR) 其它名稱:296-21257-2 |

| ADAU1761BCPZ | 制造商:Analog Devices 功能描述:IC, AUDIO CODEC, 24BIT, 96KHZ, LFCSP-32 |

| ADAU1761BCPZ-R7 | 功能描述:IC SIGMADSP CODEC PLL 32LFCSP RoHS:是 類別:集成電路 (IC) >> 接口 - 編解碼器 系列:SigmaDSP® 標準包裝:2,500 系列:- 類型:立體聲音頻 數據接口:串行 分辨率(位):18 b ADC / DAC 數量:2 / 2 三角積分調變:是 S/N 比,標準 ADC / DAC (db):81.5 / 88 動態范圍,標準 ADC / DAC (db):82 / 87.5 電壓 - 電源,模擬:2.6 V ~ 3.3 V 電壓 - 電源,數字:1.7 V ~ 3.3 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:48-WFQFN 裸露焊盤 供應商設備封裝:48-TQFN-EP(7x7) 包裝:帶卷 (TR) |

發布緊急采購,3分鐘左右您將得到回復。