- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄373983 > ADF4360-2 (Analog Devices, Inc.) Integrated Synthesizer and VCO PDF資料下載

參數(shù)資料

| 型號(hào): | ADF4360-2 |

| 廠商: | Analog Devices, Inc. |

| 元件分類(lèi): | XO, clock |

| 英文描述: | Integrated Synthesizer and VCO |

| 中文描述: | 綜合合成器和VCO |

| 文件頁(yè)數(shù): | 9/20頁(yè) |

| 文件大?。?/td> | 336K |

| 代理商: | ADF4360-2 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)當(dāng)前第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)

PRELIMINARY TECHNICAL DATA

ADF4360-2

REV. PrA 07/03

–9–

VCO

The VCO core in the ADF4360 family uses eight overlapping

bands as shown in figure 6 to allow a wide frequency range to

be covered without a large VCO sensitivity (Kv) and resultant

poor phase noise and spurious performance.

The correct band is chosen automatically by the band select

logic at power-up or whenever the N Counter latch is updated.

It is important that the correct write sequence be followed at

power-up. This sequence is:

1) R Counter latch

2) Control latch

3) N Counter latch

During band select, which takes five PFD cycles, The VCO

Vtune is disconnected from the output of the loop filter and

connected to an internal reference voltage.

The operating current in the VCO core is programmable

in four steps, 5mA, 10mA, 15mA & 20mA. This is

controlled by bits PC1 & PC2 in the Control latch.

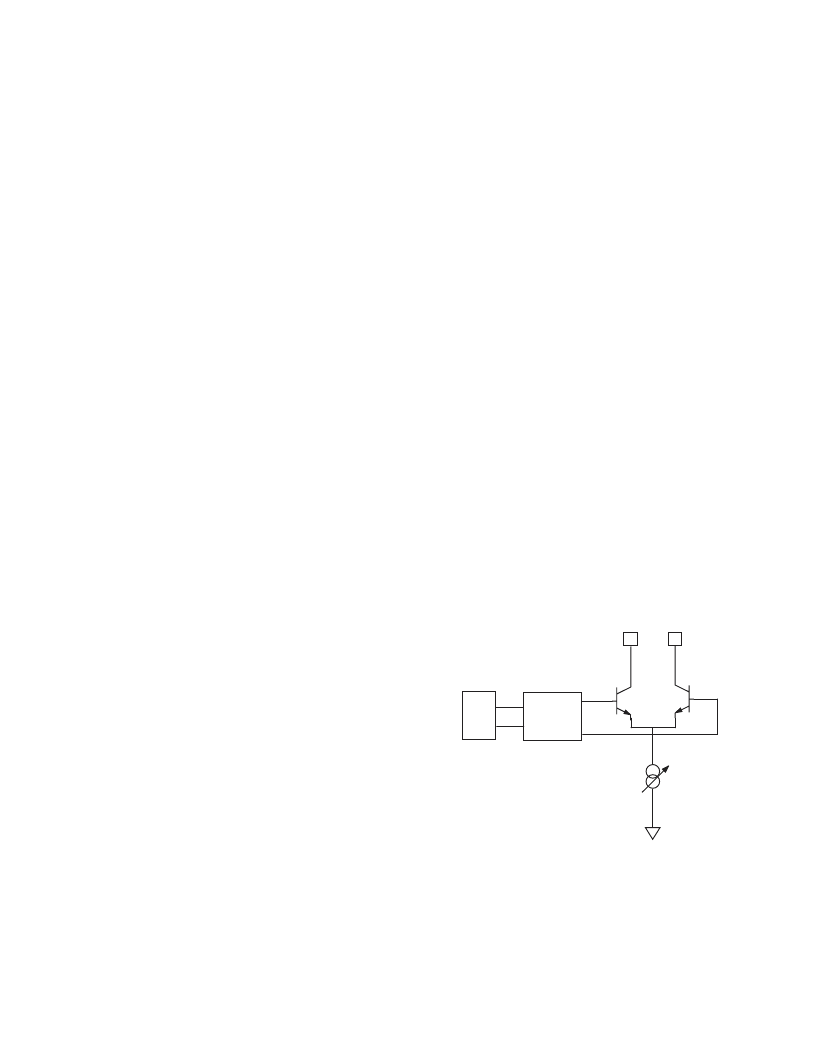

OUTPUT STAGE

The RFoutA and RFoutB pins of the ADF4360 family are

connected to the collectors of an NPN differential pair

driven by buffered outputs of the VCO as shown in figure

7. To allow the user to optimise his/her power dissipation

vs output power requirements, The tail current of the

differential pair is programmable via bits PL1 & PL2 in

the Control latch. Four current levels may be set; 3.5mA,

5mA, 7.5mA and 11mA giving output power levels of -

13dBm, -10.5dBm, -8dBm & -6dBm using a 50Ohm

resistor to Vdd and ac-coupling into a 50Ohm load.

Alternatively, both outputs can be combined in a 1+1:1

transformer or a 180 microstrip coupler. See Page 19.

If the outputs are to be used individually, then the

optimum output stage consists of a shunt inductor to Vdd.

Another feature of the ADF4360 family is provided

whereby the supply current to the RF output stage is shut

down until the part achieves lock as measured by the

Digital Lock Detect circuitry. This is enabled by the

MTLD (Mute Till Lock Detect) bit in the Control latch.

Figure 6 Frequency vs Vtune, ADF4360-2

After band select, normal PLL action resumes. The

nominal value of Kv is 57MHz/Volt or 28MHZ/Volt if

divide by two operation has been selected (by

programming DIVSEL (DB22), high in the N Counter

latch). The ADF4360 family contains linearisation

circuitry to minimise any variation of the product of Icp

and Kv.

The R Counter output is used as the clock for the band select

logic and should not exceed 1MHz. A programmable divider

is provided at the R Counter input to allow division by 1,2,4

or 8, and is controlled by bits BSC1 and BSC2 in the R

Counter Latch. Where the required PFD frequency exceeds 1

MHz the divide ratio should be set to allow enough time for

correct band selection.

VCO

BUFFER /

DIVIDE BY 2

RFOUTA

RFOUTB

Figure 7 RF Output Stage ADF4360-2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADF4360-2BCP | Integrated Synthesizer and VCO |

| ADF4360-6BCP | Integrated Synthesizer and VCO |

| ADF4360-7BCP | Integrated Synthesizer and VCO |

| ADF4360-5 | Integrated Synthesizer and VCO |

| ADF4360-5BCP | Integrated Synthesizer and VCO |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADF4360-2_12 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Integrated Synthesizer and VCO |

| ADF4360-28CPZRL7 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述: |

| ADF4360-2BCP | 制造商:Analog Devices 功能描述:PLL Frequency Synthesizer Single 24-Pin LFCSP EP 制造商:Analog Devices 功能描述:IC SYNTHESIZER PLL |

| ADF4360-2BCPRL | 制造商:Analog Devices 功能描述:PLL Frequency Synthesizer Single 24-Pin LFCSP EP T/R |

| ADF4360-2BCPRL7 | 制造商:Analog Devices 功能描述:PLL Frequency Synthesizer Single 24-Pin LFCSP EP T/R |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。