- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374016 > ADN2811ACP-CML (ANALOG DEVICES INC) OC-48/OC-48 FEC Clock and Data Recovery IC with Integrated Limiting Amp PDF資料下載

參數(shù)資料

| 型號: | ADN2811ACP-CML |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | OC-48/OC-48 FEC Clock and Data Recovery IC with Integrated Limiting Amp |

| 中文描述: | CLOCK RECOVERY CIRCUIT, QCC48 |

| 封裝: | 7 X 7 MM, LEAD FREE, MO-220-VKKD-2, LFCSP-48 |

| 文件頁數(shù): | 8/16頁 |

| 文件大小: | 359K |

| 代理商: | ADN2811ACP-CML |

REV. A

–8–

ADN2811

JITTER SPECIFICATIONS

The ADN2811 CDR is designed to achieve the best bit-error-rate

(BER) performance and has exceeded the jitter generation, trans-

fer, and tolerance specifications proposed for SONET/SDH

equipment defined in the Telcordia Technologies specification.

Jitter is the dynamic displacement of digital signal edges from

their long-term average positions measured in UI (unit intervals),

where 1 UI = 1 bit period. Jitter on the input data can cause

dynamic phase errors on the recovered clock sampling edge.

Jitter on the recovered clock causes jitter on the retimed data.

The following section briefly summarizes the specifications of

the jitter generation, transfer, and tolerance in accordance with

the Telcordia document (GR-253-CORE, Issue 3, September

2000) for the optical interface at the equipment level and the

ADN2811 performance with respect to those specifications.

Jitter Generation

The jitter generation specification limits the amount of jitter

that can be generated by the device with no jitter and wander

applied at the input. For OC-48 devices, the band-pass filter has

a 12 kHz high-pass cutoff frequency with a roll-off of 20 dB/

decade and a low-pass cutoff frequency of at least 20 MHz. The

jitter generated should be less than 0.01 UI rms and less

than 0.1 UI p-p.

Jitter Transfer

The jitter transfer function is the ratio of the jitter on the output

signal to the jitter applied on the input signal versus the fre-

quency. This parameter measures the limited amount of jitter

on an input signal that can be transferred to the output signal

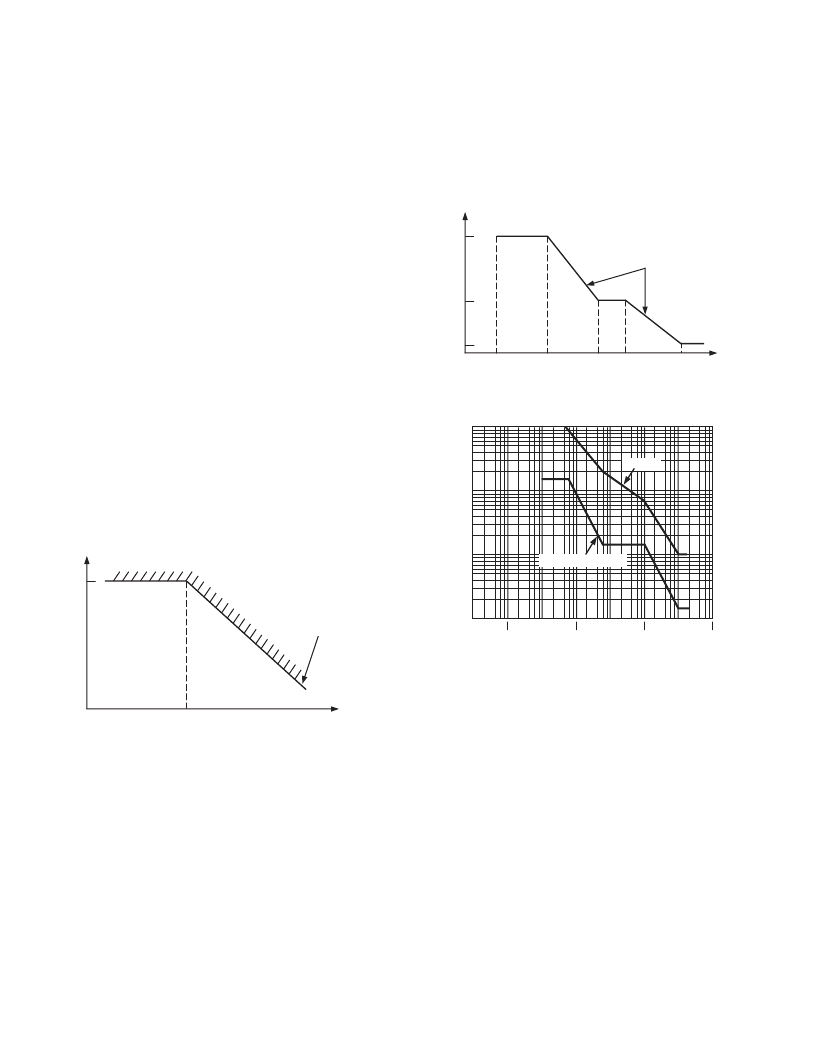

(see Figure 7).

SLOPE = –20dB/DECADE

JITTER FREQUENCY – kHz

0.1

J

f

C

ACCEPTABLE

RANGE

Figure 7. Jitter Transfer Curve

Jitter Tolerance

The jitter tolerance is defined as the peak-to-peak amplitude of

the sinusoidal jitter applied on the input signal that causes a

1 dB power penalty. This is a stress test that is intended to

ensure no additional penalty is incurred under the operating

conditions (see Figure 8). Figure 9 shows the typical OC-48

jitter tolerance performance of the ADN2811.

SLOPE = –20dB/DECADE

f

0

f

1

JITTER FREQUENCY – Hz

f

2

f

3

f

4

15

1.5

0.15

I

Figure 8. SONET Jitter Tolerance Mask

MODULATION FREQUENCY – Hz

1.00E+01

1.00E+03

1.00E+05

1.00E+07

1.00E+02

1.00E+01

1.00E–01

A

1.00E+00

1.00E+02

1.00E+04

1.00E+06

1.00E+00

ADN2811

OC-48 SONET MASK

Figure 9. OC-48 Jitter Tolerance Curve

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADN2811ACP-CML-RL | OC-48/OC-48 FEC Clock and Data Recovery IC with Integrated Limiting Amp |

| ADN2812 | Continuous Rate 12.3 Mb/s to 2.7 Gb/s Clock and Data Recovery IC with Integrated Limiting Amp |

| ADN2812ACP | Continuous Rate 12.3 Mb/s to 2.7 Gb/s Clock and Data Recovery IC with Integrated Limiting Amp |

| ADN2812ACP-RL | Continuous Rate 12.3 Mb/s to 2.7 Gb/s Clock and Data Recovery IC with Integrated Limiting Amp |

| ADN2812ACP-RL7 | Continuous Rate 12.3 Mb/s to 2.7 Gb/s Clock and Data Recovery IC with Integrated Limiting Amp |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADN2811ACP-CML-RL | 制造商:Analog Devices 功能描述:CDR 2488.32Mbps/2666.06Mbps SONET/SDH 48-Pin LFCSP EP T/R |

| ADN2811ACPZ-CML | 功能描述:IC CLK/DATA REC W/AMP 48-LFCSP RoHS:是 類別:集成電路 (IC) >> 時鐘/計時 - 專用 系列:- 標準包裝:28 系列:- 類型:時鐘/頻率發(fā)生器 PLL:是 主要目的:Intel CPU 服務(wù)器 輸入:時鐘 輸出:LVCMOS 電路數(shù):1 比率 - 輸入:輸出:3:22 差分 - 輸入:輸出:無/是 頻率 - 最大:400MHz 電源電壓:3.135 V ~ 3.465 V 工作溫度:0°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:64-TFSOP (0.240",6.10mm 寬) 供應(yīng)商設(shè)備封裝:64-TSSOP 包裝:管件 |

| ADN2811ACPZ-CML-RL | 功能描述:IC CLK DATA REC SDH 2.66GHZ 制造商:analog devices inc. 系列:- 包裝:帶卷(TR) 零件狀態(tài):上次購買時間 PLL:是 主要用途:SONET/SDH,STM 輸入:CML 輸出:CML 電路數(shù):1 比率 - 輸入:輸出:1:2 差分 - 輸入:輸出:是/是 頻率 - 最大值:2.66GHz 電壓 - 電源:3 V ~ 3.6 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:48-WFQFN 裸露焊盤 供應(yīng)商器件封裝:48-LFCSP(7x7) 標準包裝:1 |

| ADN2812 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Continuous Rate 12.3 Mb/s to 2.7 Gb/s Clock and Data Recovery IC with Integrated Limiting Amp |

| ADN2812ACP | 制造商:Analog Devices 功能描述:IC CLOCK/DATA RECOVERY |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。