- 您現在的位置:買賣IC網 > PDF目錄374016 > ADN2819 (Analog Devices, Inc.) Multirate to 2.7 Gb/s Clock and Data Recovery IC with Integrated Limiting Amp PDF資料下載

參數資料

| 型號: | ADN2819 |

| 廠商: | Analog Devices, Inc. |

| 元件分類: | 運動控制電子 |

| 英文描述: | Multirate to 2.7 Gb/s Clock and Data Recovery IC with Integrated Limiting Amp |

| 中文描述: | 多速率為2.7 Gb / s的集成時鐘和數據恢復芯片限幅放大器 |

| 文件頁數: | 15/24頁 |

| 文件大小: | 570K |

| 代理商: | ADN2819 |

ADN2819

Rev. B | Page 15 of 24

100k

100k

BUFFER

ADN2819

VCC/2

REFCLKN

REFCLKP

CRYSTAL

OSCILLATOR

XO1

XO2

REFSEL

NC

19.44MHz

VCC

0

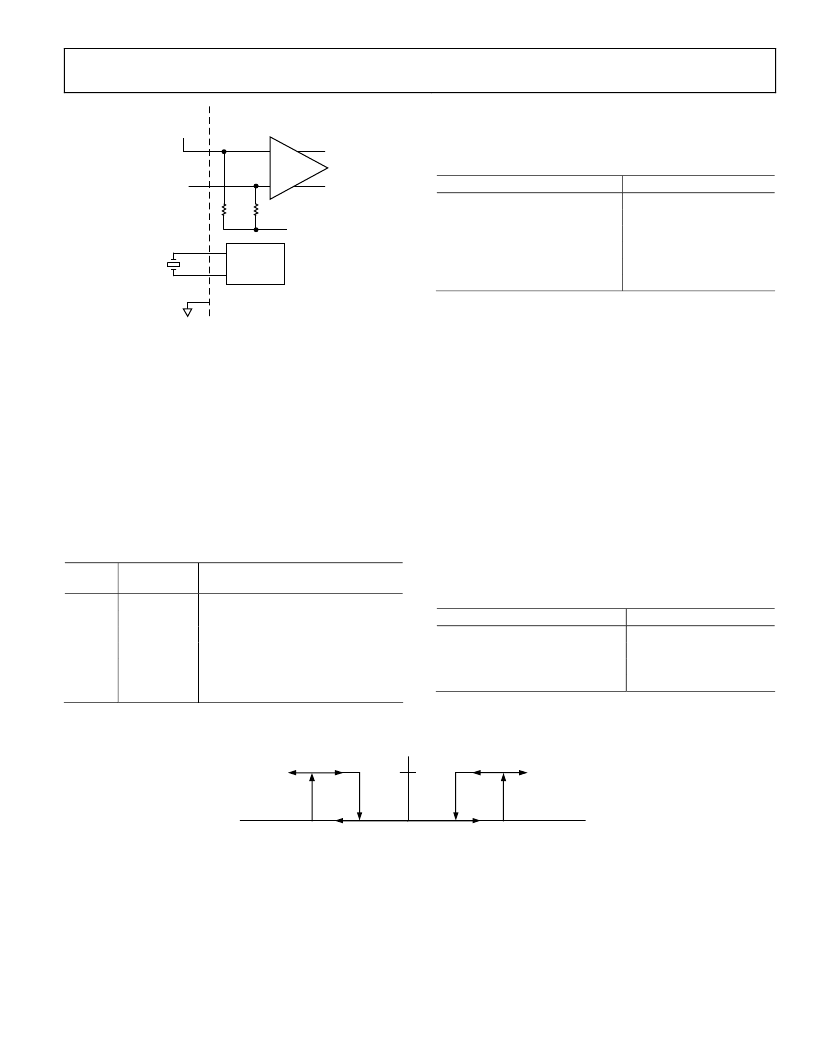

Figure 19. Crystal Oscillator Configuration

The ADN2819 can accept any of the following reference clock

frequencies: 19.44 MHz, 38.88 MHz, and 77.76 MHz at LVTTL/

LVCMOS/LVPECL/LVDS levels, or 155.52 MHz at LVPECL/

LVDS levels via the REFCLKN/P inputs, independent of data

rate (including Gigabit Ethernet and wrapper rates). The input

buffer accepts any differential signal with a peak-to-peak

differential amplitude of greater than 100 mV (e.g., LVPECL or

LVDS) or a standard single-ended low voltage TTL input,

providing maximum system flexibility. The appropriate division

ratio can be selected using the REFSEL0/1 pins, according to

Table 6. Phase noise and duty cycle of the reference clock are

not critical, and 100 ppm accuracy is sufficient.

Table 6. Reference Frequency Selection

Applied Reference Frequency

(MHz)

1

00

19.44

1

01

38.88

1

10

77.76

1

11

155.52

0

XX

REFCLKP/N Inactive. Use 19.44 MHz

XTAL on Pins XO1, XO2 (pull REFCLKP

to VCC)

REFSEL

REFSEL[1..0]

An on-chip oscillator to be used with an external crystal is also

provided as an alternative to using the REFCLKN/P inputs.

Details of the recommended crystal are given in Table 7.

Table 7. Required Crystal Specifications

Parameter

Mode

Frequency/Overall Stability

Frequency Accuracy

Temperature Stability

Aging

ESR

Value

Series Resonant

19.44 MHz ± 100 ppm

±100 ppm

±100 ppm

±100 ppm

50 max

REFSEL must be tied to VCC when the REFCLKN/P inputs are

active, or tied to VEE when the oscillator is used. No connection

between the XO pin and the REFCLK input is necessary (see

Figure 17, Figure 18, and Figure 19). Note that the crystal should

operate in series resonant mode, which renders it insensitive to

external parasitics. No trimming capacitors are required.

LOCK DETECTOR OPERATION

The lock detector monitors the frequency difference between

the VCO and the reference clock, and deasserts the loss of lock

signal when the VCO is within 500 ppm of center frequency.

This enables the phase loop, which then maintains phase lock,

unless the frequency error exceeds 0.1%. Should this occur, the

loss of lock signal is reasserted and control returns to the fre-

quency loop, which will reacquire and maintain a stable clock

signal at the output. The frequency loop requires a single exter-

nal capacitor between CF1 and CF2. The capacitor specification

is given in Table 8.

Table 8. Recommended C

F

Capacitor Specification

Parameter

Temperature Range

Capacitance

Leakage

Rating

Value

–40°C to +85°C

>3.0 μF

<80 nA

>6.3 V

1000

500

0

500

1000

f

ERROR

(ppm)

LOL

1

0

Figure 20. Transfer Function LOL

相關PDF資料 |

PDF描述 |

|---|---|

| ADN2819ACP-CML | Multirate to 2.7 Gb/s Clock and Data Recovery IC with Integrated Limiting Amp |

| ADN2819ACP-CML-RL | Multirate to 2.7 Gb/s Clock and Data Recovery IC with Integrated Limiting Amp |

| ADN2819ACPZ-CML-RL1 | Multirate to 2.7 Gb/s Clock and Data Recovery IC with Integrated Limiting Amp |

| ADN2819ACPZ-CML1 | Multirate to 2.7 Gb/s Clock and Data Recovery IC with Integrated Limiting Amp |

| ADN2830ACP32-REEL | Circular Connector; No. of Contacts:4; Series:LJT06R; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:21; Circular Contact Gender:Socket; Circular Shell Style:Straight Plug; Insert Arrangement:21-75 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADN2819ACP-CML | 制造商:Analog Devices 功能描述:CDR 2488.32Mbps/2666.06Mbps SONET/SDH 48-Pin LFCSP EP Tray 制造商:Rochester Electronics LLC 功能描述:MULTI-RATE 2.7GBPS CDR/ PA LOW POWER I.C - Bulk |

| ADN2819ACP-CML-RL | 制造商:Analog Devices 功能描述:CDR 2488.32Mbps/2666.06Mbps SONET/SDH 48-Pin LFCSP EP T/R |

| ADN2819ACPZ-CML | 功能描述:IC CLOCK/DATA RECOVERY 48LFCSP RoHS:是 類別:集成電路 (IC) >> 時鐘/計時 - 專用 系列:- 標準包裝:28 系列:- 類型:時鐘/頻率發生器 PLL:是 主要目的:Intel CPU 服務器 輸入:時鐘 輸出:LVCMOS 電路數:1 比率 - 輸入:輸出:3:22 差分 - 輸入:輸出:無/是 頻率 - 最大:400MHz 電源電壓:3.135 V ~ 3.465 V 工作溫度:0°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:64-TFSOP (0.240",6.10mm 寬) 供應商設備封裝:64-TSSOP 包裝:管件 |

| ADN2819ACPZ-CML1 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Multirate to 2.7 Gb/s Clock and Data Recovery IC with Integrated Limiting Amp |

| ADN2819ACPZ-CML-RL | 功能描述:IC CLOCK/DATA RECOVERY 48LFCSP RoHS:是 類別:集成電路 (IC) >> 時鐘/計時 - 專用 系列:- 標準包裝:28 系列:- 類型:時鐘/頻率發生器 PLL:是 主要目的:Intel CPU 服務器 輸入:時鐘 輸出:LVCMOS 電路數:1 比率 - 輸入:輸出:3:22 差分 - 輸入:輸出:無/是 頻率 - 最大:400MHz 電源電壓:3.135 V ~ 3.465 V 工作溫度:0°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:64-TFSOP (0.240",6.10mm 寬) 供應商設備封裝:64-TSSOP 包裝:管件 |

發布緊急采購,3分鐘左右您將得到回復。