- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374032 > ADSP-2104LKP-55 (ANALOG DEVICES INC) Low Cost DSP Microcomputers PDF資料下載

參數(shù)資料

| 型號: | ADSP-2104LKP-55 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | Low Cost DSP Microcomputers |

| 中文描述: | 24-BIT, 13.824 MHz, OTHER DSP, PQCC68 |

| 封裝: | PLASTIC, LCC-68 |

| 文件頁數(shù): | 6/36頁 |

| 文件大小: | 333K |

| 代理商: | ADSP-2104LKP-55 |

第1頁第2頁第3頁第4頁第5頁當前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁

ADSP-2104/ADSP-2109

–6–

REV. 0

CLKIN

CLKOUT

XTAL

ADSP-2104/

ADSP-2109

Figure 2. External Crystal Connections

A clock output signal (CLK OUT ) is generated by the processor,

synchronized to the processor’s internal cycles.

Reset

The RESET

signal initiates a complete reset of the processor.

T he

RESET

signal must be asserted when the chip is powered

up to assure proper initialization. If the

RESET

signal is applied

during initial power-up, it must be held long enough to allow

the processor’s internal clock to stabilize. If

RESET

is activated

at any time after power-up and the input clock frequency does

not change, the processor’s internal clock continues and does

not require this stabilization time.

T he power-up sequence is defined as the total time required for

the crystal oscillator circuit to stabilize after a valid V

DD

is

applied to the processor and for the internal phase-locked loop

(PLL) to lock onto the specific crystal frequency. A minimum of

2000 t

CK

cycles will ensure that the PLL has locked (this does

not, however, include the crystal oscillator start-up time).

During this power-up sequence the

RESET

signal should be

held low. On any subsequent resets, the

RESET

signal must

meet the minimum pulse width specification, t

RSP

.

T o generate the

RESET

signal, use either an RC circuit with an

external Schmidt trigger or a commercially available reset IC.

(Do not use only an RC circuit.)

T he

RESET

input resets all internal stack pointers to the empty

stack condition, masks all interrupts, and clears the MST AT

register. When

RESET

is released, the boot loading sequence is

performed (provided there is no pending bus request and the

chip is configured for booting, with MMAP = 0). T he first

instruction is then fetched from internal program memory

location 0x0000.

Program Memory Interface

T he on-chip program memory address bus (PMA) and on-chip

program memory data bus (PMD) are multiplexed with the on-

chip data memory buses (DMA, DMD), creating a single

external data bus and a single external address bus. T he external

data bus is bidirectional and is 24 bits wide to allow instruction

fetches from external program memory. Program memory may

contain code and data.

T he external address bus is 14 bits wide.

T he data lines are bidirectional. T he program memory select

(

PMS

) signal indicates accesses to program memory and can be

used as a chip select signal. T he write (

WR

) signal indicates a

write operation and is used as a write strobe. T he read (

RD

)

signal indicates a read operation and is used as a read strobe or

output enable signal.

T he processor writes data from the 16-bit registers to 24-bit

program memory using the PX register to provide the lower

eight bits. When the processor reads 16-bit data from 24-bit

program memory to a 16-bit data register, the lower eight bits

are placed in the PX register.

T he program memory interface can generate 0 to 7 wait states

for external memory devices; default is to 7 wait states after

RESET

.

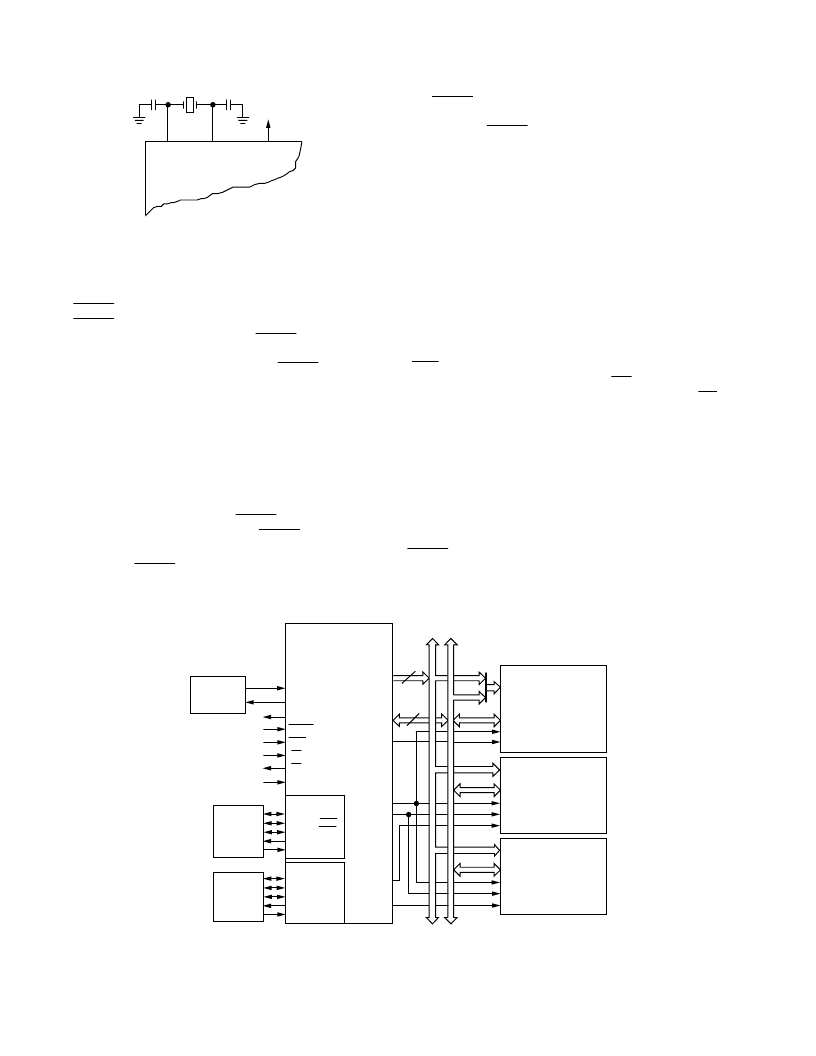

Figure 3. ADSP-2104/ADSP-2109 System

BR

BG

CLKIN

RESET

IRQ2

BMS

ADSP-2104

or

ADSP-2109

CLKOUT

ADDR

DATA

OE

WE

CS

(OPTIONAL)

1x CLOCK

or

CRYSTAL

PMS

DMS

RD

WR

ADDR

13-0

DATA

23-0

ADDR

DATA

OE

WE

CS

(OPTIONAL)

ADDR

DATA

OE

CS

BOOT

MEMORY

e.g. EPROM

2764

27128

27256

27512

PROGRAM

MEMORY

DATA

MEMORY

&

PERIPHERALS

14

24

D23-22

A13-0

D

15-8

D

23-0

D

23-8

A

13-0

A

13-0

XTAL

MMAP

SERIAL

DEVICE

(OPTIONAL)

SCLK1

RFS1 orIRQ0

TFS1 orIRQ1

DT1 or FO

DR1 or FI

SCLK0

RFS0

TFS0

DT0

DR0

SPORT 1

SPORT 0

SERIAL

DEVICE

(OPTIONAL)

THE TWO MSBs OF THE DATA BUS (D

) ARE USED TO SUPPLY THE TWO MSBs OF THE

BOOT MEMORY EPROM ADDRESS. THIS IS ONLY REQUIRED FOR THE 27256 AND 27512.

相關PDF資料 |

PDF描述 |

|---|---|

| ADSP-21160M | DSP Microcomputer |

| ADSP-21160MKB-80 | DSP Microcomputer |

| ADSP-21160NKB-95 | DSP Microcomputer |

| ADSP-21160N | Cap-Free, NMOS, 150mA Low Dropout Regulator with Reverse Current Protection |

| ADSP-21160NCB-TBD | Cap-Free, NMOS, 150mA Low Dropout Regulator with Reverse Current Protection |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| ADSP2105 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:(666.40 k) |

| ADSP-2105 | 制造商:AD 制造商全稱:Analog Devices 功能描述:ADSP-2100 Family DSP Microcomputers |

| ADSP-2105BP-55 | 制造商:Analog Devices 功能描述:DSP Fixed-Point 16-Bit 13.824MHz 13.824MIPS 68-Pin PLCC 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| ADSP-2105BP-55REEL | 制造商:Rochester Electronics LLC 功能描述:- Tape and Reel |

| ADSP-2105BP-80 | 功能描述:IC DSP CONTROLLER 16BIT 68PLCC RoHS:否 類別:集成電路 (IC) >> 嵌入式 - DSP(數(shù)字式信號處理器) 系列:ADSP-21xx 標準包裝:2 系列:StarCore 類型:SC140 內(nèi)核 接口:DSI,以太網(wǎng),RS-232 時鐘速率:400MHz 非易失內(nèi)存:外部 芯片上RAM:1.436MB 電壓 - 輸入/輸出:3.30V 電壓 - 核心:1.20V 工作溫度:-40°C ~ 105°C 安裝類型:表面貼裝 封裝/外殼:431-BFBGA,F(xiàn)CBGA 供應商設備封裝:431-FCPBGA(20x20) 包裝:托盤 |

發(fā)布緊急采購,3分鐘左右您將得到回復。