- 您現在的位置:買賣IC網 > PDF目錄374032 > ADSP-21065 (Analog Devices, Inc.) Cap-Free, NMOS, 150mA Low Dropout Regulator with Reverse Current Protection PDF資料下載

參數資料

| 型號: | ADSP-21065 |

| 廠商: | Analog Devices, Inc. |

| 元件分類: | 基準電壓源/電流源 |

| 英文描述: | Cap-Free, NMOS, 150mA Low Dropout Regulator with Reverse Current Protection |

| 中文描述: | 無電容,NMOS管,150mA的低壓差穩壓器的反向電流保護 |

| 文件頁數: | 24/44頁 |

| 文件大小: | 331K |

| 代理商: | ADSP-21065 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁

REV. B

ADSP-21065L

–24–

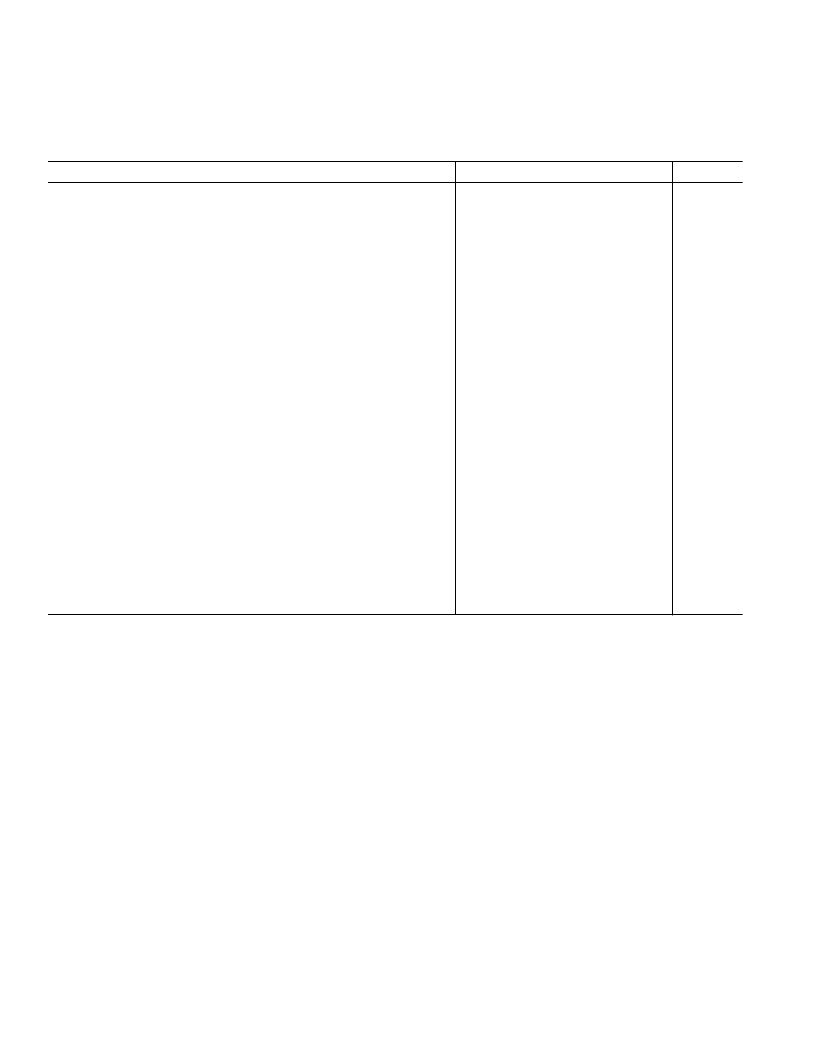

Asynchronous Read/Write—Host to ADSP-21065L

Use these specifications for asynchronous host processor accesses of an ADSP-21065L, after the host has asserted

CS

and

HBR

(low). After the ADSP-21065L returns

HBG

, the host can drive the

RD

and

WR

pins to access the ADSP-21065L’s IOP registers.

HBR

and

HBG

are assumed low for this timing. Writes can occur at a minimum interval of (1/2) t

CK

.

Parameter

Min

Max

Units

Read Cycle

Timing Requirements:

t

SADRDL

t

HADRDH

t

WRWH

t

DRDHRDY

t

DRDHRDY

Address Setup

/

CS

Low Before

RD

Low*

Address Hold/

CS

Hold Low After

RD

High

RD

/

WR

High Width

RD

High Delay After REDY (O/D) Disable

RD

High Delay After REDY (A/D) Disable

0.0

0.0

6.0

0.0

0.0

ns

ns

ns

ns

ns

Switching Characteristics:

t

SDATRDY

t

DRDYRDL

t

RDYPRD

t

HDARWH

Data Valid Before REDY Disable from Low

REDY (O/D) or (A/D) Low Delay After

RD

Low

REDY (O/D) or (A/D) Low Pulsewidth for Read

Data Disable After

RD

High

1.5

ns

ns

ns

ns

13.5

28.0 + DT

2.0

10.0

Write Cycle

Timing Requirements:

t

SCSWRL

t

HCSWRH

t

SADWRH

t

HADWRH

t

WWRL

t

WRWH

t

DWRHRDY

t

SDATWH

t

HDATWH

CS

Low Setup Before

WR

Low

CS

Low Hold After

WR

High

Address Setup Before

WR

High

Address Hold After

WR

High

WR

Low Width

RD

/

WR

High Width

WR

High Delay After REDY (O/D) or (A/D) Disable

Data Setup Before

WR

High

Data Hold After

WR

High

0.0

0.0

5.0

2.0

7.0

6.0

0.0

5.0

1.0

ns

ns

ns

ns

ns

ns

ns

ns

ns

Switching Characteristics:

t

DRDYWRL

t

RDYPWR

REDY (O/D) or (A/D) Low Delay After

WR

/

CS

Low

REDY (O/D) or (A/D) Low Pulsewidth for Write

13.5

ns

ns

7.75

NOTE

*Not required if

RD

and address are valid t

after

HBG

goes low. For first access after

HBR

asserted, ADDR23-0 must be a nonMMS value 1/2 t

before

RD

or

WR

goes low or by t

after

HBG

goes low. This is easily accomplished by driving an upper address signal high when

HBG

is asserted. See Host Interface, in

the

ADSP-21065L SHARC User’s Manual

, Second Edition.

相關PDF資料 |

PDF描述 |

|---|---|

| ADSP-21065L | Cap-Free, NMOS, 150mA Low Dropout Regulator with Reverse Current Protection |

| ADSP-21065LKCA-240 | DSP Microcomputer |

| ADSP-21065LKCA-264 | DSP Microcomputer |

| ADSP-2109KP-80 | Low Cost DSP Microcomputers |

| ADSP-2109LKP-55 | Low Cost DSP Microcomputers |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADSP-21065L | 制造商:AD 制造商全稱:Analog Devices 功能描述:DSP Microcomputer |

| ADSP-21065LCCA-240 | 功能描述:IC DSP CTLR 32BIT 196CSPBGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - DSP(數字式信號處理器) 系列:SHARC® 標準包裝:2 系列:StarCore 類型:SC140 內核 接口:DSI,以太網,RS-232 時鐘速率:400MHz 非易失內存:外部 芯片上RAM:1.436MB 電壓 - 輸入/輸出:3.30V 電壓 - 核心:1.20V 工作溫度:-40°C ~ 105°C 安裝類型:表面貼裝 封裝/外殼:431-BFBGA,FCBGA 供應商設備封裝:431-FCPBGA(20x20) 包裝:托盤 |

| ADSP-21065LCCAZ240 | 功能描述:IC DSP CTLR 32BIT 196CSPBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - DSP(數字式信號處理器) 系列:SHARC® 標準包裝:2 系列:StarCore 類型:SC140 內核 接口:DSI,以太網,RS-232 時鐘速率:400MHz 非易失內存:外部 芯片上RAM:1.436MB 電壓 - 輸入/輸出:3.30V 電壓 - 核心:1.20V 工作溫度:-40°C ~ 105°C 安裝類型:表面貼裝 封裝/外殼:431-BFBGA,FCBGA 供應商設備封裝:431-FCPBGA(20x20) 包裝:托盤 |

| ADSP-21065LCS-240 | 制造商:Analog Devices 功能描述:DSP Floating-Point 32-Bit 60MHz 60MIPS 208-Pin MQFP 制造商:Analog Devices 功能描述:IC MICROCOMPUTER 32-BIT |

| ADSP-21065LCSZ-240 | 功能描述:IC DSP CONTROLLER 32BIT 208-MQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - DSP(數字式信號處理器) 系列:SHARC® 標準包裝:40 系列:TMS320DM64x, DaVinci™ 類型:定點 接口:I²C,McASP,McBSP 時鐘速率:400MHz 非易失內存:外部 芯片上RAM:160kB 電壓 - 輸入/輸出:3.30V 電壓 - 核心:1.20V 工作溫度:0°C ~ 90°C 安裝類型:表面貼裝 封裝/外殼:548-BBGA,FCBGA 供應商設備封裝:548-FCBGA(27x27) 包裝:托盤 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

發布緊急采購,3分鐘左右您將得到回復。