- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374035 > ADSP-2173BS-80 (ANALOG DEVICES INC) DSP Microcomputer PDF資料下載

參數(shù)資料

| 型號: | ADSP-2173BS-80 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | DSP Microcomputer |

| 中文描述: | 24-BIT, 10 MHz, OTHER DSP, PQFP128 |

| 封裝: | PLASTIC, QFP-128 |

| 文件頁數(shù): | 9/52頁 |

| 文件大小: | 664K |

| 代理商: | ADSP-2173BS-80 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

ADSP-2171/ADSP-2172/ADSP-2173

REV. A

–9–

Stand-Alone ROM E xecution

When the MMAP and BMODE pins both are set to 1, the

ROM is automatically enabled and execution commences from

program memory location 0x0800 at the start of ROM. T his

feature lets an embedded design operate without external

memory components. T o operate in this mode, the ROM coded

program must copy an interrupt vector table to the appropriate

locations in program memory RAM. In this mode, the ROM

enable bit defaults to 1 during reset.

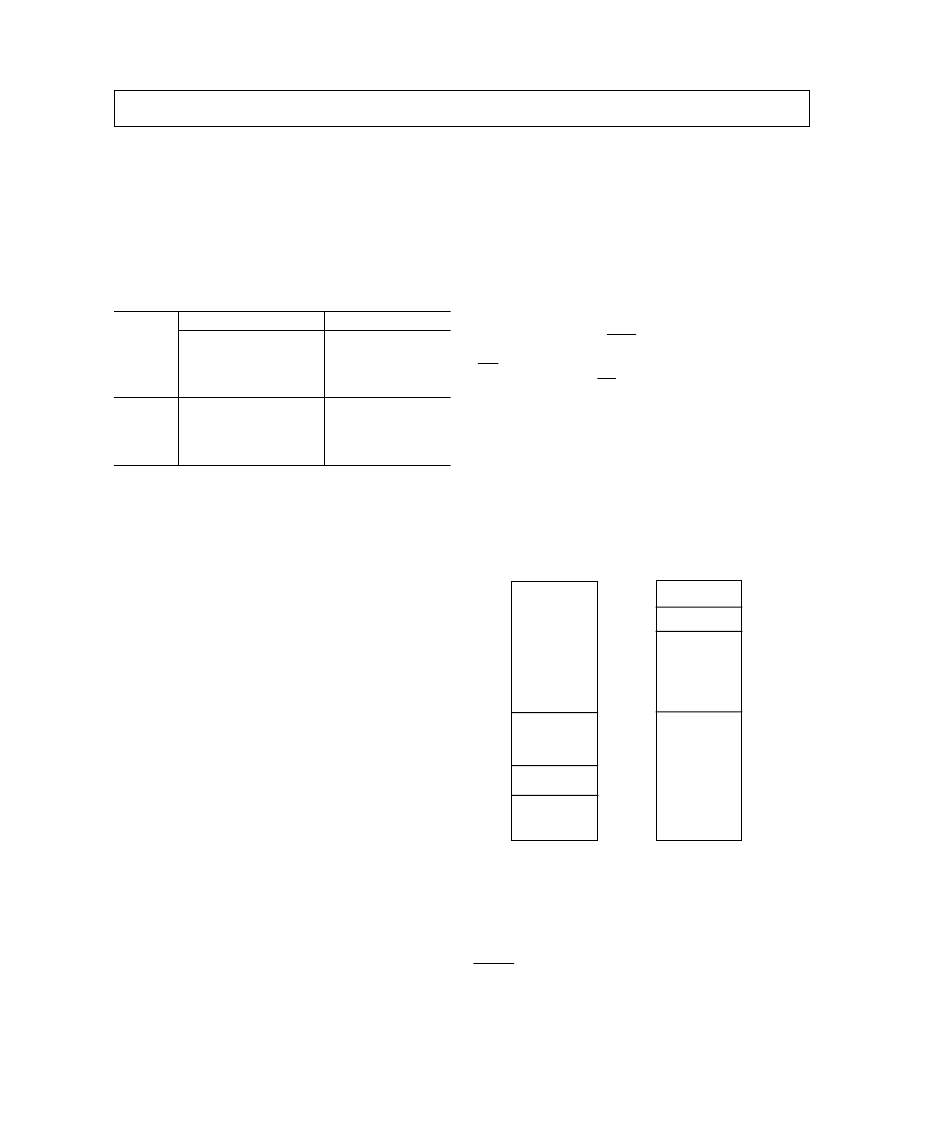

T able III. Boot Summary T able

BMODE = 0

BMODE = 1

MMAP = 0

Boot from EPROM,

then execution starts

at internal RAM

location 0x0000

Boot from HIP, then

execution starts at

internal RAM location

0x0000

MMAP = 1

No booting, execution

starts at external memory

location 0x0000

Stand-Alone Mode,

execution starts at

internal ROM location

0x0800

Ordering Procedure for ADSP-2172 Processors

T o place an order for a custom ROM-coded ADSP-2172 pro-

cessor, you must:

1. Complete the following forms contained in the

ADSP ROM

Ordering Package

, available from your Analog Devices sales

representative:

ADSP-2172 ROM Specification Form

ROM Release Agreement

ROM NRE Agreement & Minimum Quantity Order (MQO)

Acceptance Agreement for Pre-production ROM Products.

2. Return the forms to Analog Devices along with two copies of

the Memory Image File (.EX E file) of your ROM code. T he

files must be supplied on two 3.5" or 5.25" floppy disks for

IBM PC (DOS 2.01 or higher).

3. Place a purchase order with Analog Devices for nonrecurring

engineering charges (NRE) associated with ROM product

development.

After this information is received, it is entered into Analog

Devices’ ROM Manager System which assigns a custom ROM

model number to the product. T his model number will be

branded on all prototype and production units manufactured to

these specifications.

T o minimize the risk of code being altered during this process,

Analog Devices verifies that the .EX E files on both floppy disks are

identical, and recalculates the checksums for the .EX E file en-

tered into the ROM Manager System. T he checksum data, in the

form of a ROM memory map, a hard copy of the .EX E file, and a

ROM Data Verification Form are returned to you for inspection.

A signed ROM Verification Form and a purchase order for pro-

duction units are required prior to any product being manufac-

tured. Prototype units may be applied toward the minimum

order quantity.

Upon completion of the prototype manufacture, Analog Devices

will ship prototype units and a delivery schedule update for pro-

duction units. An invoice against your purchase order for the

NRE charges is issued at this time.

T here is a charge for each ROM mask generated and a mini-

mum order quantity. Consult your sales representative for

details. A separate order must be placed for parts of a specific

package type, temperature range, and speed grade.

Data Memory Interface

T he data memory address (DMA) bus is 14 bits wide. T he bidi-

rectional external data bus is 24 bits wide, with the upper 16

bits (D8–D23) used for data memory data (DMD) transfers.

T he data memory select (

DMS

) signal indicates access to the

data memory and can be used as a chip select signal. T he write

(

WR

) signal indicates a write operation and can be used as a

write strobe. T he read (

RD

) signal indicates a read operation

and can be used as a read strobe or output enable signal.

T he ADSP-217x supports memory-mapped I/O, with the pe-

ripherals memory mapped into the data or program memory ad-

dress spaces and accessed by the processor in the same manner.

Data Memory Map

T he on-chip data memory RAM resides in the 2K words of data

memory beginning at address 0x3000, as shown in Figure 6. In

addition, data memory locations from 0x3800 to the end of data

memory at 0x3FFF are reserved. Control registers for the sys-

tem, timer, wait state configuration, host interface port, and se-

rial port operations are located in this region of memory.

3BFF

3C00

37FF

3800

DATA MEMORY

12K

EXTERNAL

3FFF

0000

2FFF

3000

1K

RESERVED

MEMORY MAPPED

REGISTERS/

RESERVED

2K

INTERNAL

DATA RAM

03FF

0400

07FF

0800

WAIT STATES

DWAIT 2

(10K EXTERNAL)

3FFF

0000

2FFF

3000

NO WAIT

STATES

DWAIT 0

(1K EXTERNAL)

DWAIT 1

(1K EXTERNAL)

Figure 6. ADSP-217x Data Memory Map

T he remaining 12K of data memory is external. External data

memory is divided into three zones, each associated with its own

wait state generator. By mapping peripherals into different

zones, you can accommodate peripherals with different wait

state requirements. All zones default to 7 wait states after

RESET

. For compatibility with other ADSP-2100 Family pro-

cessors, bit definitions for DWAIT 3 and DWAIT 4 are shown

in the Data Memory Wait State Control Register, but they are

not used by the ADSP-217x.

相關PDF資料 |

PDF描述 |

|---|---|

| ADSP-2171 | DSP Microcomputer(DSP 微計算機) |

| ADSP-2172 | DSP Microcomputer(DSP 微計算機) |

| ADSP-2173 | DSP Microcomputer(DSP 微計算機) |

| ADSP-2181BS-115 | DSP Microcomputer |

| ADSP-2181BS-133 | DSP Microcomputer |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| ADSP-2173BST-80 | 制造商:Analog Devices 功能描述:DSP Fixed-Point 16-Bit 20MHz 20MIPS 128-Pin TQFP 制造商:Rochester Electronics LLC 功能描述:16BIT FXD PT PROC 3.3V - Bulk |

| ADSP-2176-760040 | 制造商:Analog Devices 功能描述: |

| ADSP-2176-760061 | 制造商:Analog Devices 功能描述: |

| ADSP-2176-760243 | 制造商:Analog Devices 功能描述: |

| ADSP-2178-780244 | 制造商:AD 制造商全稱:Analog Devices 功能描述:GSM Baseband Processing Chipset |

發(fā)布緊急采購,3分鐘左右您將得到回復。