- 您現在的位置:買賣IC網 > PDF目錄374036 > ADSP-2185L (Analog Devices, Inc.) LM2941/LM2941C 1A Low Dropout Adjustable Regulator; Package: CERDIP; No of Pins: 16; Qty per Container: 25; Container: Rail PDF資料下載

參數資料

| 型號: | ADSP-2185L |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | LM2941/LM2941C 1A Low Dropout Adjustable Regulator; Package: CERDIP; No of Pins: 16; Qty per Container: 25; Container: Rail |

| 中文描述: | DSP的微機 |

| 文件頁數: | 5/31頁 |

| 文件大小: | 223K |

| 代理商: | ADSP-2185L |

第1頁第2頁第3頁第4頁當前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁

ADSP-2185L

–5–

REV. A

Pin Terminations (Continued)

I/O

3-State

(Z)

Hi-Z*

Caused

By

Pin

Name

Reset

State

Unused

Configuration

D4 or

IS

D3 or

IACK

D2:0 or

IAD15:13

PMS

DMS

BMS

IOMS

CMS

RD

WR

BR

BG

BGH

IRQ2

/PF7

I/O (Z)

I

I/O (Z)

Hi-Z

I

Hi-Z

BR

,

EBR

Float

High (Inactive)

Float

Float

Float

Float

Float

Float

Float

Float

Float

Float

Float

High (Inactive)

Float

Float

Input = High (Inactive)

or Program as Output,

Set to 1, Let Float

Input = High (Inactive)

or Program as Output,

Set to 1, Let Float

Input = High (Inactive)

or Program as Output,

Set to 1, Let Float

Input = High (Inactive)

or Program as Output,

Set to 1, Let Float

Input = High or Low,

Output = Float

High or Low

High or Low

High or Low

Float

Input = High or Low,

Output = Float

High or Low

High or Low

High or Low

Float

BR

,

EBR

I/O (Z)

I/O (Z)

O (Z)

O (Z)

O (Z)

O (Z)

O (Z)

O (Z)

O (Z)

I

O (Z)

O

I/O (Z)

Hi-Z

Hi-Z

O

O

O

O

O

O

O

I

O

O

I

BR

,

EBR

IS

BR, EBR

BR

,

EBR

BR

,

EBR

BR

,

EBR

BR

,

EBR

BR

,

EBR

BR

,

EBR

EE

IRQL1

/PF6 I/O (Z)

I

IRQL0

/PF5 I/O (Z)

I

IRQE

/PF4

I/O (Z)

I

SCLK0

I/O

I

RFS0

DR0

TFS0

DT0

SCLK1

I/O

I

I/O

O

I/O

I

I

O

O

I

RFS1/

RQ0

DR1/FI

TFS1/

RQ1

DT1/FO

EE

EBR

EBG

ERESET

EMS

EINT

ECLK

ELIN

ELOUT

I/O

I

I/O

O

I

I

O

I

O

I

I

I

O

I

I

O

O

I

I

O

I

O

I

I

I

O

NOTES

*

*Hi-Z = High Impedance.

1.If the CLKOUT pin is not used, turn it OFF.

2.If the Interrupt/Programmable Flag pins are not used, there are two options:

Option 1: When these pins are configured as INPUTS at reset and function as

interrupts and input flag pins, pull the pins High (inactive).

Option 2: Program the unused pins as OUTPUTS, set them to 1, and let

them float.

3.All bidirectional pins have three-stated outputs. When the pins is configured

as an output, the output is Hi-Z (high impedance) when inactive.

4.CLKIN, RESET, and PF3:0 are not included in the table because these pins

must be used.

Interrupts

The interrupt controller allows the processor to respond to the

eleven possible interrupts and reset with minimum overhead.

The ADSP-2185L provides four dedicated external interrupt

input pins,

IRQ2

,

IRQL0

,

IRQL1

and

IRQE

. In addition,

SPORT1 may be reconfigured for

IRQ0

,

IRQ1

, FLAG_IN and

FLAG_OUT, for a total of six external interrupts. The ADSP-

2185L also supports internal interrupts from the timer, the byte

DMA port, the two serial ports, software and the power-down

control circuit. The interrupt levels are internally prioritized and

individually maskable (except power down and reset). The

IRQ2

,

IRQ0

and

IRQ1

input pins can be programmed to be

either level- or edge-sensitive.

IRQL0

and

IRQL1

are level-

sensitive and

IRQE

is edge sensitive. The priorities and vector

addresses of all interrupts are shown in Table I.

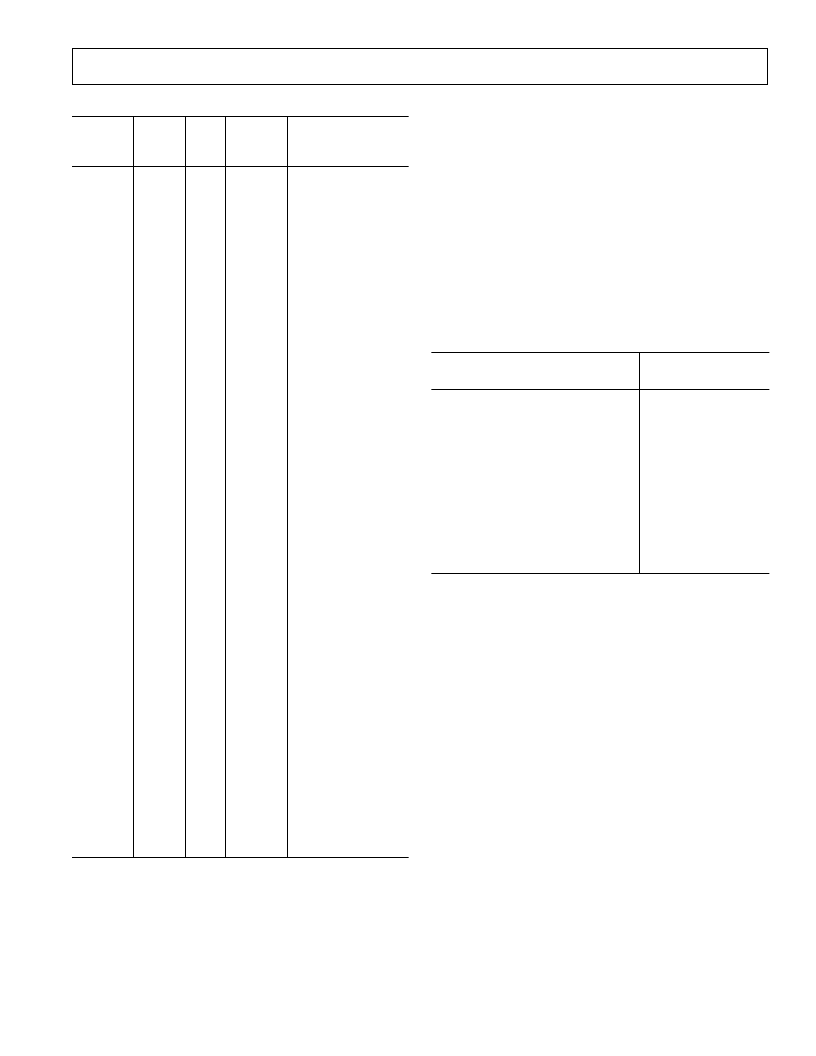

Table I. Interrupt Priority and Interrupt Vector Addresses

Interrupt Vector

Address (Hex)

Source of Interrupt

RESET

(or Power-Up with PUCR = 1)

Power-Down (Nonmaskable)

IRQ2

IRQL1

IRQL0

SPORT0 Transmit

SPORT0 Receive

IRQE

BDMA Interrupt

SPORT1 Transmit or

IRQ1

SPORT1 Receive or

IRQ0

Timer

0000 (

Highest Priority

)

002C

0004

0008

000C

0010

0014

0018

001C

0020

0024

0028 (

Lowest Priority

)

Interrupt routines can either be nested with higher priority inter-

rupts taking precedence or processed sequentially. Interrupts

can be masked or unmasked with the IMASK register. Indi-

vidual interrupt requests are logically ANDed with the bits in

IMASK; the highest priority unmasked interrupt is then se-

lected. The power-down interrupt is nonmaskable.

The ADSP-2185L masks all interrupts for one instruction cycle

following the execution of an instruction that modifies the

IMASK register. This does not affect serial port auto-

buffering or DMA transfers.

The interrupt control register, ICNTL, controls interrupt nest-

ing and defines the

IRQ0

,

IRQ1

and

IRQ2

external interrupts to

be either edge- or level-sensitive. The

IRQE

pin is an external

edge-sensitive interrupt and can be forced and cleared. The

IRQL0

and

IRQL1

pins are external level-sensitive interrupts.

The IFC register is a write-only register used to force and clear

interrupts. On-chip stacks preserve the processor status and are

automatically maintained during interrupt handling. The stacks are

twelve levels deep to allow interrupt, loop and subroutine nest-

ing. The following instructions allow global enable or disable

servicing of the interrupts (including power down), regardless of

the state of IMASK. Disabling the interrupts does not affect se-

rial port autobuffering or DMA.

ENA INTS;

DIS INTS;

When the processor is reset, interrupt servicing is enabled.

相關PDF資料 |

PDF描述 |

|---|---|

| ADSP-2185LBST-160 | DSP Microcomputer |

| ADSP-2185LBST-210 | DSP Microcomputer |

| ADSP-2185NBCA-320 | LM2941/LM2941C 1A Low Dropout Adjustable Regulator; Package: TO-263; No of Pins: 5; Qty per Container: 45; Container: Rail |

| ADSP-2185NBST-320 | DSP Microcomputer |

| ADSP-2185BST-115 | DSP Microcomputer |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADSP-2185LBCA-210 | 制造商:Analog Devices 功能描述:DSP Fixed-Point 16-Bit 52.5MHz 52.5MIPS 144-Pin CSP-BGA 制造商:Rochester Electronics LLC 功能描述:16K/16K 16BIT DSP 3.3V 52 MIPS MINI BGA - Bulk |

| ADSP-2185LBST-115 | 制造商:Analog Devices 功能描述:DSP Fixed-Point 16-Bit 28.8MHz 28.8MIPS 100-Pin LQFP |

| ADSP-2185L-BST-133 | 制造商:Analog Devices 功能描述: |

| ADSP-2185LBST-133 | 制造商:Rochester Electronics LLC 功能描述:3.3V 16BIT DSP,33MIPS,16KWRDSPM/DM,100TQ - Bulk 制造商:Analog Devices 功能描述:IC MICROCOMPUTER 16-BIT |

| ADSP-2185LBST-160 | 制造商:Analog Devices 功能描述:DSP Fixed-Point 16-Bit 40MHz 40MIPS 100-Pin LQFP 制造商:Rochester Electronics LLC 功能描述:16K/16K 16 BIT DSP 40 MIPS 3.3 V - Bulk |

發布緊急采購,3分鐘左右您將得到回復。