- 您現在的位置:買賣IC網 > PDF目錄374037 > ADSP-BF531SBBZ400 (ANALOG DEVICES INC) Blackfin Embedded Processor PDF資料下載

參數資料

| 型號: | ADSP-BF531SBBZ400 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 數字信號處理 |

| 英文描述: | Blackfin Embedded Processor |

| 中文描述: | 16-BIT, 40 MHz, OTHER DSP, PBGA169 |

| 封裝: | ROHS COMPLIANT, PLASTIC, MO-034AAG-2, BGA-169 |

| 文件頁數: | 13/56頁 |

| 文件大小: | 671K |

| 代理商: | ADSP-BF531SBBZ400 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁

ADSP-BF531/ADSP-BF532/ADSP-BF533

Rev. 0

|

Page 13 of 56

|

March 2004

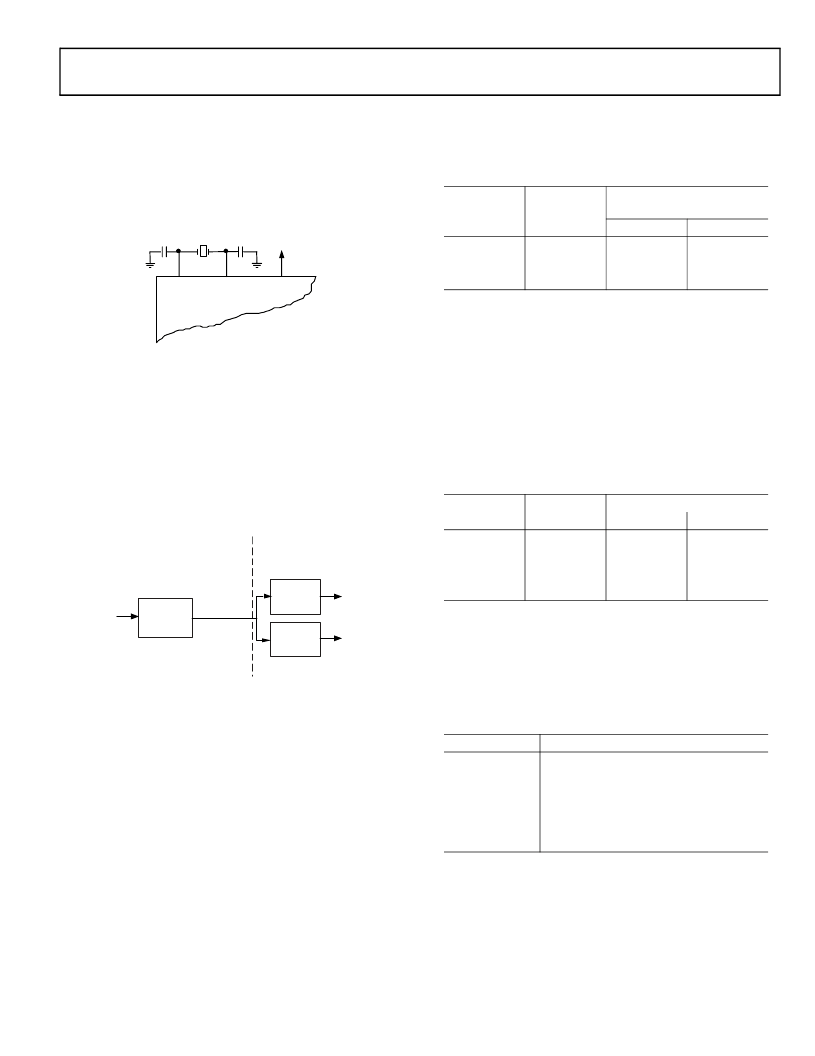

Alternatively, because the ADSP-BF531/2/3 processor includes

an on-chip oscillator circuit, an external crystal may be used.

The crystal should be connected across the CLKIN and XTAL

pins, with two capacitors connected as shown in

Figure 8

.

Capacitor values are dependent on crystal type and should be

specified by the crystal manufacturer. A parallel-resonant,

fundamental frequency, microprocessor-grade crystal should be

used.

As shown in

Figure 9 on Page 13

, the core clock (CCLK) and

system peripheral clock (SCLK) are derived from the input

clock (CLKIN) signal. An on-chip PLL is capable of multiplying

the CLKIN signal by a user programmable 1x to 63x multiplica-

tion factor (bounded by specified minimum and maximum

VCO frequencies). The default multiplier is 10x, but it can be

modified by a software instruction sequence. On-the-fly fre-

quency changes can be effected by simply writing to the

PLL_DIV register.

All on-chip peripherals are clocked by the system clock (SCLK).

The system clock frequency is programmable by means of the

SSEL3–0 bits of the PLL_DIV register. The values programmed

into the SSEL fields define a divide ratio between the PLL output

(VCO) and the system clock. SCLK divider values are 1 through

15.

Table 6

illustrates typical system clock ratios.

The maximum frequency of the system clock is f

SCLK

. Note that

the divisor ratio must be chosen to limit the system clock fre-

quency to its maximum of f

SCLK

. The SSEL value can be changed

dynamically without any PLL lock latencies by writing the

appropriate values to the PLL divisor register (PLL_DIV).

The core clock (CCLK) frequency can also be dynamically

changed by means of the CSEL1–0 bits of the PLL_DIV register.

Supported CCLK divider ratios are 1, 2, 4, and 8, as shown in

Table 7

. This programmable core clock capability is useful for

fast core frequency modifications.

BOOTING MODES

The ADSP-BF531/2/3 processor has two mechanisms (listed in

Table 8

) for automatically loading internal L1 instruction mem-

ory after a reset. A third mode is provided to execute from

external memory, bypassing the boot sequence.

Figure 8. External Crystal Connections

Figure 9. Frequency Modification Methods

CLKIN

CLKOUT

XTAL

PLL

0.5

×

- 64

×

÷ 1:15

÷ 1, 2, 4, 8

VCO

SCLK

≤

CCLK

SCLK

≤

133MHZ

CLKIN

“FINE” ADJUSTMENT

REQUIRES PLL SEQUENCING

“COARSE” ADJUSTMENT

ON-THE-FLY

CCLK

SCLK

Table 6. Example System Clock Ratios

Signal Name

SSEL3–0

Divider Ratio

VCO/SCLK

Example Frequency Ratios

(MHz)

VCO

100

400

500

SCLK

100

133

50

0001

0011

1010

1:1

3:1

10:1

Table 7. Core Clock Ratios

Signal Name

CSEL1–0

Divider Ratio

VCO/CCLK

Example Frequency Ratios

VCO

300

300

500

200

CCLK

300

150

125

25

00

01

10

11

1:1

2:1

4:1

8:1

Table 8. Booting Modes

BMODE1–0

00

Description

Execute from 16-Bit External Memory (Bypass

Boot ROM)

Boot from 8-Bit or 16-Bit FLASH

Reserved

Boot from SPI Serial EEPROM (8-, 16-, or 24-Bit

address range)

01

10

11

相關PDF資料 |

PDF描述 |

|---|---|

| ADSP-BF531SBST400 | Circular Connector Series:97 |

| ADSP-BF532 | Blackfin Embedded Processor |

| ADSP-BF532SBBC400 | Blackfin Embedded Processor |

| ADSP-BF532SBBZ400 | Blackfin Embedded Processor |

| ADSP-BF532SBST400 | 28-2 (14 Contacts) Pin Insert; For Use With:Amphenol MIL-C-5015 97 Series Circular Connectors; No. of Contacts:14; Gender:Male; Operating Voltage:1250V |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADSP-BF531SBST-300 | 制造商:Analog Devices 功能描述: |

| ADSP-BF531SBST-300X | 制造商:Analog Devices 功能描述: |

| ADSP-BF531SBST400 | 制造商:Analog Devices 功能描述:DSP Fixed-Point 16-Bit 400MHz 400MIPS 176-Pin LQFP 制造商:Rochester Electronics LLC 功能描述:DUAL MAC16-BIT400MHZ,52KB SRAM - Bulk 制造商:Analog Devices 功能描述:IC MICROCOMPUTER 16-BIT |

| ADSP-BF531SBST-C81 | 制造商:Analog Devices 功能描述: |

| ADSP-BF531SBST-ENG | 制造商:Analog Devices 功能描述: |

發布緊急采購,3分鐘左右您將得到回復。