- 您現在的位置:買賣IC網 > PDF目錄374044 > ADV202BBC-115 (ANALOG DEVICES INC) Circular Connector; No. of Contacts:22; Series:LJTP02R; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:13; Circular Contact Gender:Pin; Circular Shell Style:Box Mount Receptacle; Insert Arrangement:13-35 PDF資料下載

參數資料

| 型號: | ADV202BBC-115 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 消費家電 |

| 英文描述: | Circular Connector; No. of Contacts:22; Series:LJTP02R; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:13; Circular Contact Gender:Pin; Circular Shell Style:Box Mount Receptacle; Insert Arrangement:13-35 |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PBGA121 |

| 封裝: | 12 X 12 MM, MO-192-ABD-1, CSPBGA-121 |

| 文件頁數: | 30/40頁 |

| 文件大小: | 841K |

| 代理商: | ADV202BBC-115 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁當前第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

ADV202

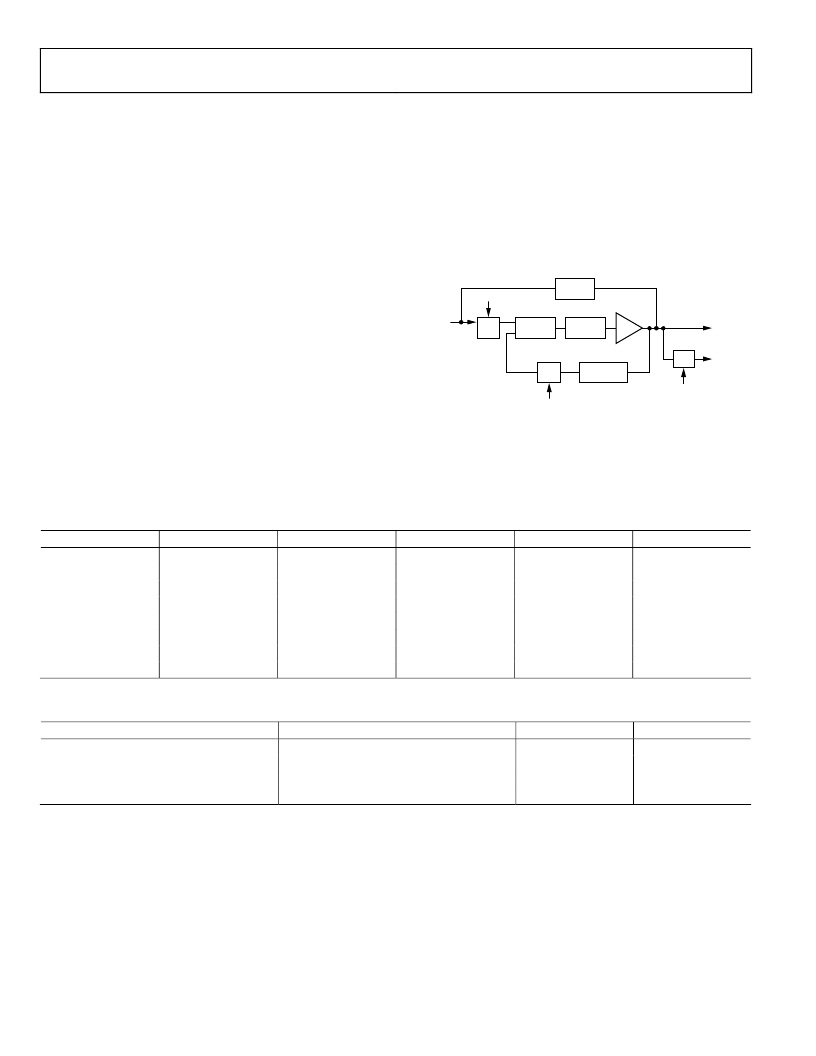

PLL

The ADV202 uses the PLL_HI and PLL_LO direct registers to

configure the PLL. Any time the PLL_LO register is modified,

the host must wait at least 20 μs before reading or writing any

other register. If this delay is not implemented, erratic behavior

might result.

Rev. 0 | Page 30 of 40

The PLL can be programmed to have any possible final

multiplier value as long as

JCLK > 50 MHz and < 150 MHz (144-pin version).

JCLK > 50 MHz and < 115 MHz (121-pin version).

HCLK < 115 MHz.

JCLK ≥ 2 × VCLK for single-component input.

JCLK ≥ 2 × VCLK for YCrCb [4:2:2] input.

In JDATA mode (JDATA), JCLK must be 4 × MCLK or

higher.

The maximum burst frequency for external DMA modes is

≤ 0.36 JCLK.

For MCLK frequencies greater than 50 MHz, the input clock

divider must be enabled, that is, IPD set to 1.

IPD cannot be enabled for MCLK frequencies below 20 MHz.

To achieve the lowest power consumption, an MCLK frequency

of 27 MHz is recommended for a standard definition CCIR656

input. The PLL circuit is recommended to have a multiplier of 3.

This sets JCLK and HCLK to 81 MHz.

0

LPF

PHASE

DETECT

VCO

JCLK

HCLK

÷

2

HCLKD

÷

PLLMULT

÷

2

LFB

÷

2

IPD

BYPASS

MCLK

Figure 24. PLL Architecture and Control Functions

Table 20. Recommended PLL Register Settings

IPD

LFB

0

0

0

0

0

1

0

1

1

0

1

0

1

1

1

1

PLLMULT

N

N

N

N

N

N

N

N

HCLKD

0

1

0

1

0

1

0

1

HCLK

N × MCLK

N × MCLK/2

2 × N × MCLK

N × MCLK

N × MCLK/2

N × MCLK/4

N × MCLK

N × MCLK/2

JCLK

N × MCLK

N × MCLK

2 × N × MCLK

2 × N × MCLK

N × MCLK/2

N × MCLK/2

N × MCLK

N × MCLK

Table 21. Recommended Values for PLL_HI and PLL_LO Registers

Video Standard

SMPTE125M or ITU-R.BT656 (NTSC or PAL)

SMPTE293M (525p)

ITU-R.BT1358 (625p)

SMPTE274M (1080i)

CLKIN Frequency on MCLK

27 MHz

27 MHz

27 MHz

74.25 MHz

PLL_HI

0x0008

0x0008

0x0008

0x0008

PLL_LO

0x0004

0x0004

0x0004

0x0084

相關PDF資料 |

PDF描述 |

|---|---|

| ADV202BBC-150 | Circular Connector; No. of Contacts:22; Series:LJTP02R; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:13; Circular Contact Gender:Pin; Circular Shell Style:Box Mount Receptacle; Insert Arrangement:13-35 |

| ADV202BBCZ-115 | Circular Connector; No. of Contacts:22; Series:LJTP02R; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:13; Circular Contact Gender:Socket; Circular Shell Style:Box Mount Receptacle |

| ADV3000 | 3:1 HDMI/DVI Switch with Equalization |

| ADV3000ASTZ | 3:1 HDMI/DVI Switch with Equalization |

| ADV3000ASTZ-RL | 3:1 HDMI/DVI Switch with Equalization |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADV202BBC-135 | 制造商:Analog Devices 功能描述:Video CODEC 144-Pin CSP-BGA 制造商:Rochester Electronics LLC 功能描述:JPEG 2000 CODEC CONVERTER - Bulk |

| ADV202BBC-150 | 制造商:Analog Devices 功能描述:Video CODEC 144-Pin CSP-BGA 制造商:Rochester Electronics LLC 功能描述:JPEG 2000 CODEC CONVERTER - Bulk 制造商:Analog Devices 功能描述:IC VIDEO CODEC |

| ADV202BBCZ-115 | 功能描述:IC VIDEO CODEC JPEG2000 121-BGA RoHS:是 類別:集成電路 (IC) >> 接口 - 編解碼器 系列:- 標準包裝:2,500 系列:- 類型:立體聲音頻 數據接口:串行 分辨率(位):18 b ADC / DAC 數量:2 / 2 三角積分調變:是 S/N 比,標準 ADC / DAC (db):81.5 / 88 動態范圍,標準 ADC / DAC (db):82 / 87.5 電壓 - 電源,模擬:2.6 V ~ 3.3 V 電壓 - 電源,數字:1.7 V ~ 3.3 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:48-WFQFN 裸露焊盤 供應商設備封裝:48-TQFN-EP(7x7) 包裝:帶卷 (TR) |

| ADV202BBCZ-135 | 功能描述:IC CODEC VIDEO 135MHZ 144CSPBGA RoHS:是 類別:集成電路 (IC) >> 接口 - 編解碼器 系列:- 標準包裝:2,500 系列:- 類型:立體聲音頻 數據接口:串行 分辨率(位):18 b ADC / DAC 數量:2 / 2 三角積分調變:是 S/N 比,標準 ADC / DAC (db):81.5 / 88 動態范圍,標準 ADC / DAC (db):82 / 87.5 電壓 - 電源,模擬:2.6 V ~ 3.3 V 電壓 - 電源,數字:1.7 V ~ 3.3 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:48-WFQFN 裸露焊盤 供應商設備封裝:48-TQFN-EP(7x7) 包裝:帶卷 (TR) |

| ADV202BBCZ-150 | 功能描述:IC VIDEO CODEC JPEG2000 144CSBGA RoHS:是 類別:集成電路 (IC) >> 接口 - 編解碼器 系列:- 標準包裝:2,500 系列:- 類型:立體聲音頻 數據接口:串行 分辨率(位):18 b ADC / DAC 數量:2 / 2 三角積分調變:是 S/N 比,標準 ADC / DAC (db):81.5 / 88 動態范圍,標準 ADC / DAC (db):82 / 87.5 電壓 - 電源,模擬:2.6 V ~ 3.3 V 電壓 - 電源,數字:1.7 V ~ 3.3 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:48-WFQFN 裸露焊盤 供應商設備封裝:48-TQFN-EP(7x7) 包裝:帶卷 (TR) |

發布緊急采購,3分鐘左右您將得到回復。