- 您現在的位置:買賣IC網 > PDF目錄374044 > ADV601JS (ANALOG DEVICES INC) Low Cost Multiformat Video Codec PDF資料下載

參數資料

| 型號: | ADV601JS |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 消費家電 |

| 英文描述: | Low Cost Multiformat Video Codec |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP160 |

| 封裝: | PLASTIC, QFP-160 |

| 文件頁數: | 24/52頁 |

| 文件大小: | 606K |

| 代理商: | ADV601JS |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

ADV601

–24–

REV. 0

Video Formats — Multiplexed Philips Video

The ADV601 supports a hybrid mode of operation that is a cross

between standard dual lane Philips and single lane CCIR-656. In

this mode, video data is multiplexed in the same fashion in CCIR-656,

but the values 0 and 255 are not reserved as signaling values. In-

stead, external HSYNC and VSYNC pins are used for signaling

and video synchronization. VCLK may range up to 29.5 MHz.

VCLK is driven with up to a 29.5 MHz 50% duty cycle clock

synchronous with the video data. Video data is clocked on the

rising edge of the VCLK signal. The functionality of HSYNC,

VSYNC, and FIELD pins is dependent on three programmable

modes of the ADV601: Master-Slave Control, Encode-Decode

Control, and 525-625 Control. Table XI summarizes the func-

tionality of these pins in various modes.

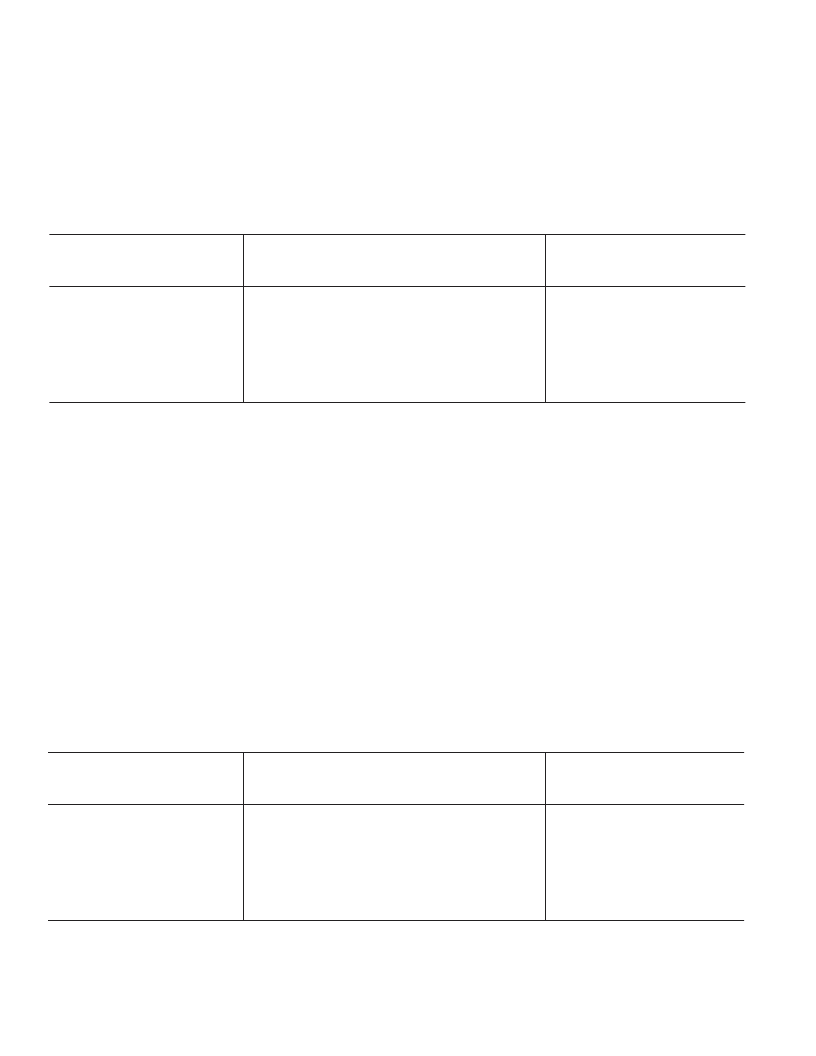

Table XI. Philips Multiplexed Video Master and Slave Modes HSYNC, VSYNC, and FIELD Functionality

HSYNC, VSYNC and FIELD

Functionality for Multiplexed

Philips

Master Mode (HSYNC, VSYNC

and FIELD Are Outputs)

Slave Mode (HSYNC, VSYNC

and FIELD Are Inputs)

Encode Mode (video data is input

to the chip)

The ADV601 completely manages the generation and

timing of these pins. The device driving the ADV601

video interface must use these outputs to remain in

sync with the ADV601. It is expected that this com-

bination of modes would not be used frequently.

The ADV601 completely manages the generation

and timing of these pins.

These pins are used to control the

blanking of video and sequencing.

Decode Mode (video data is output

from the chip)

These pins are used to control the

blanking of video and sequencing.

Video Formats — Gray Scale Video

The Gray Scale video format requires 4:0:0 data (up to 12 bits)

be transmitted over a one “lane” 8- to 12-bit physical interface.

A video clock (typically 27 MHz) is transmitted along with the

data. This clock is synchronous with the data and runs at twice

the transfer rate of the interface. The color space is Gray Scale.

Because the ADV601 internal processing is not dependent on

color space, Gray Scale data is processed in the same manner as

data in other color spaces.

VCLK is driven with a 24.54 MHz–29.5 MHz, 50% duty cycle

clock which is synchronous with the video data. Video data is

clocked on the second rising edge of the VCLK signal.

These video formats require external synchronization and

blanking signals to accompany digital video. These signals are

VSYNC, HSYNC, and FIELD. In general, when the ADV601

is configured as an encoder, these signals will all be inputs.

When the ADV601 is configured as a decoder, these signals will

be outputs. There are special cases for this format described in

Table XII.

Table XII. Gray Scale Video Master and Slave Modes HSYNC, VSYNC and FIELD Functionality

HSYNC, VSYNC, and FIELD

Functionality for Gray Scale

Format

Master Mode (HSYNC, VSYNC,

CREF and FIELD Are Outputs)

Slave Mode (HSYNC, VSYNC,

CREF and FIELD Are Inputs)

Encode Mode (video data is input

to the chip)

The ADV601 completely manages the generation and

timing of these pins. The device driving the ADV601

video interface must use these outputs to remain in

sync with the ADV601. It is expected that this com-

bination of modes would not be used frequently.

The ADV601 completely manages the generation

and timing of these pins.

These pins are used to control the

blanking of video and sequencing.

Decode Mode (video data is output

from the chip)

These pins are used to control the

blanking of video and sequencing.

Video Formats—References

For more information on video interface standards, see the

following reference texts.

For the definition of CCIR-601:

1992 –

CCIR Recommendations RBT series Broadcasting Service

(Television)

Rec. 601-3

Encoding Parameters of digital television

for studios

, page 35, September 15, 1992.

For the definition of CCIR-656:

1992 –

CCIR Recommendations RBT series Broadcasting Service

(Television) Rec. 656-1 Interfaces for digital component video

signals in 525 and 626 line television systems operating at the

4:2:2 level of Rec. 601

, page 46, September 15, 1992.

相關PDF資料 |

PDF描述 |

|---|---|

| ADV601LC | Ultralow Cost Video Codec |

| ADV601LCJST | Ultralow Cost Video Codec |

| ADV7120KP30 | CMOS 80 MHz, Triple 8-Bit Video DAC |

| ADV7120 | CMOS 80 MHz, Triple 8-Bit Video DAC |

| ADV7120KP50 | CMOS 80 MHz, Triple 8-Bit Video DAC |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADV601JS12 | 制造商:Analog Devices 功能描述:Multiformat Video Codec 160-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:DIGITAL VIDEO CODEC REV 1.2 - Bulk |

| ADV601LC | 制造商:AD 制造商全稱:Analog Devices 功能描述:Ultralow Cost Video Codec |

| ADV601LCERAG1266B-0.5 | 制造商:Analog Devices 功能描述: |

| ADV601LCJST | 制造商:Analog Devices 功能描述:Ultralow Cost Video Codec 120-Pin LQFP 制造商:Analog Devices 功能描述:IC VIDEO CODEC |

| ADV601LCJSTRL | 制造商:Analog Devices 功能描述:Ultralow Cost Video Codec 120-Pin LQFP T/R |

發布緊急采購,3分鐘左右您將得到回復。