- 您現在的位置:買賣IC網 > PDF目錄374044 > ADV601LCJST (ANALOG DEVICES INC) Ultralow Cost Video Codec PDF資料下載

參數資料

| 型號: | ADV601LCJST |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 消費家電 |

| 英文描述: | Ultralow Cost Video Codec |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP120 |

| 封裝: | LQFP-120 |

| 文件頁數: | 16/52頁 |

| 文件大小: | 606K |

| 代理商: | ADV601LCJST |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

ADV601

–16–

REV. 0

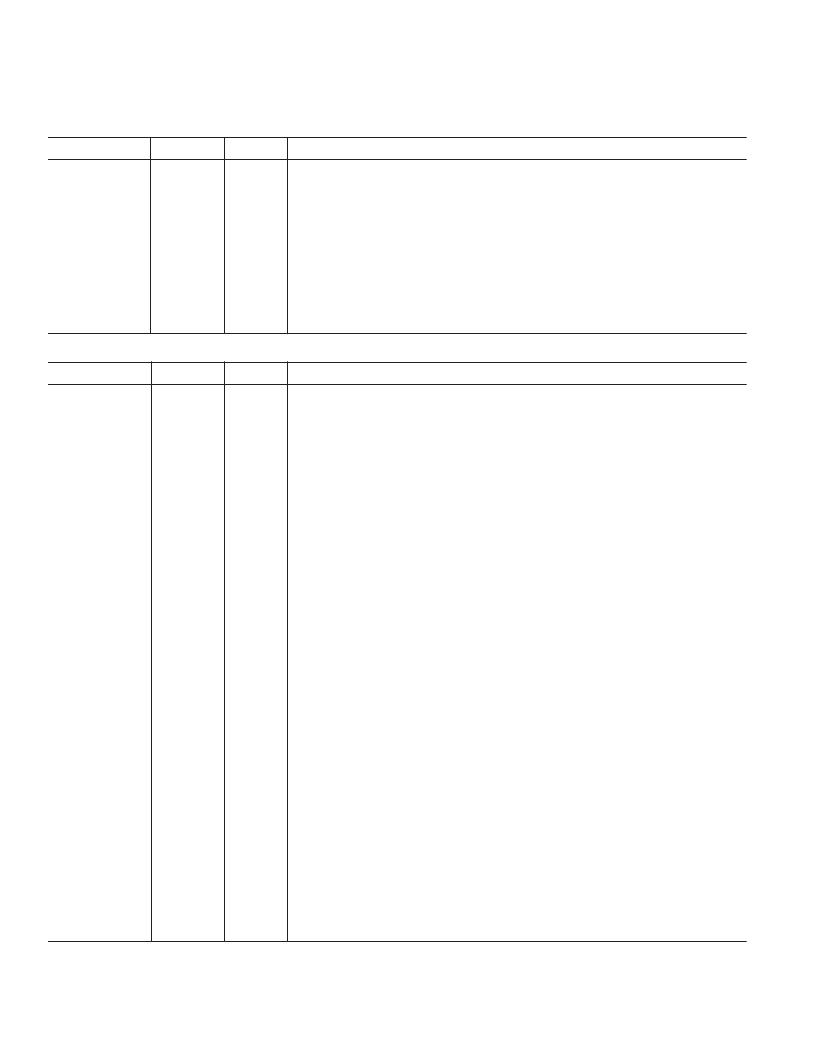

PIN FUNCTION DESCRIPTIONS

Clock Pins

Name

VCLK/XTAL

Pins

2

I/O

I

Description

A single clock (VCLK) or crystal input (across VCLK and XTAL). Acceptable 50%

duty cycle clock signals are as follows:

24.54 MHz (Square Pixel NTSC)

27 MHz (CCIR601 NTSC/PAL)

29.5 MHz (Square Pixel PAL)

If using a clock crystal, use a parallel resonant, microprocessor grade clock crystal. If

using a clock input, use a TTL level input, 50% duty cycle clock with 1 ns (or less)

jitter (measured rising edge to rising edge). Slowly varying, low jitter clocks are

acceptable; up to 5% frequency variation in 0.5 sec.

VCLK Output or VCLK Output divided by two. Select function using Mode

Control register.

VCLKO

1

O

Video Interface Pins

Name

VSYNC

Pins

1

I/O

I or O

Description

Vertical Sync or Vertical Blank. This pin can be either an output (Master Mode) or

an input (Slave Mode). The pin operates as follows:

Output (Master) HI during inactive lines of video and LO otherwise

Input (Slave) a HI on this input indicates inactive lines of video

Horizontal Sync or Horizontal Blank. This pin can be either an output (Master

Mode) or an input (Slave Mode). The pin operates as follows:

Output (Master) HI during inactive portion of video line and LO otherwise

Input (Slave) a HI on this input indicates inactive portion of video line

Note that the polarity of this signal is modified using the Mode Control register. For

detailed timing information, see the Video Interface section.

Field # or Frame Sync. This pin can be either an output (Master Mode) or an input

(Slave Mode). The pin operates as follows:

Output (Master) HI during Field1 lines of video and LO otherwise

Input (Slave) a HI on this input indicates Field1 lines of video

Encode or Decode. This output pin indicates the coding mode of the ADV601 and

operates as follows:

LO Decode Mode (Video Interface is output)

HI Encode Mode (Video Interface is input)

Note that this pin can be used to control bus enable pins for devices connected to

the ADV601 Video Interface.

4:2:2 Video Data (8-, 10-, or 12-bit digital component video data). These pins are

inputs during encode mode and outputs during decode mode. When outputs (de-

code) these pins are compatible with 50 pF loads (rather than 30 pF as all other

busses) to meet the high performance and large number of typical loads on this bus.

The performance of these pins varies with the Video Interface Mode set in the

Mode Control register, see the Video Interface section of this data sheet for pin

assignments in each mode.

Note that the Mode Control register also sets whether the color component is

treated as either signed or unsigned.

Clock Reference pin for Philips Interface (VCLK qualifier)—This pin can be either

an output (Master Mode) or an input (Slave Mode). The pin operates as follows:

Output (Master) HI to qualify VCLK during VCLK phases containing valid de-

multiplexed digital video and LO otherwise

Input (Slave) a HI on this input qualifies VCLK during VCLK phases containing

valid de-multiplexed digital video.

HSYNC

1

I or O

FIELD

1

I or O

ENC

1

O

VDATA[19:0]

20

I/O

CREF

1

I/O

相關PDF資料 |

PDF描述 |

|---|---|

| ADV7120KP30 | CMOS 80 MHz, Triple 8-Bit Video DAC |

| ADV7120 | CMOS 80 MHz, Triple 8-Bit Video DAC |

| ADV7120KP50 | CMOS 80 MHz, Triple 8-Bit Video DAC |

| ADV7120KP80 | CMOS 80 MHz, Triple 8-Bit Video DAC |

| ADV7120KST30 | CMOS 80 MHz, Triple 8-Bit Video DAC |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADV601LCJSTRL | 制造商:Analog Devices 功能描述:Ultralow Cost Video Codec 120-Pin LQFP T/R |

| ADV601LCJSTZ | 功能描述:IC CODEC VIDEO DSP/SRL 120LQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 編解碼器 系列:- 標準包裝:2,500 系列:- 類型:立體聲音頻 數據接口:串行 分辨率(位):18 b ADC / DAC 數量:2 / 2 三角積分調變:是 S/N 比,標準 ADC / DAC (db):81.5 / 88 動態范圍,標準 ADC / DAC (db):82 / 87.5 電壓 - 電源,模擬:2.6 V ~ 3.3 V 電壓 - 電源,數字:1.7 V ~ 3.3 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:48-WFQFN 裸露焊盤 供應商設備封裝:48-TQFN-EP(7x7) 包裝:帶卷 (TR) |

| ADV601LCJSTZRL | 功能描述:IC CODEC VIDEO DSP/SRL 120LQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 編解碼器 系列:- 標準包裝:2,500 系列:- 類型:立體聲音頻 數據接口:串行 分辨率(位):18 b ADC / DAC 數量:2 / 2 三角積分調變:是 S/N 比,標準 ADC / DAC (db):81.5 / 88 動態范圍,標準 ADC / DAC (db):82 / 87.5 電壓 - 電源,模擬:2.6 V ~ 3.3 V 電壓 - 電源,數字:1.7 V ~ 3.3 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:48-WFQFN 裸露焊盤 供應商設備封裝:48-TQFN-EP(7x7) 包裝:帶卷 (TR) |

| ADV601LC-VIDEOPIPE | 制造商:Analog Devices 功能描述:TOOLS:DEVELOPMENT BOARDS H/W 制造商:Analog Devices 功能描述:EVALUATION BOARD ((NS)) |

| ADV601XS | 制造商:Analog Devices 功能描述: |

發布緊急采購,3分鐘左右您將得到回復。