- 您現在的位置:買賣IC網 > PDF目錄374044 > ADV601LCJST (ANALOG DEVICES INC) Ultralow Cost Video Codec PDF資料下載

參數資料

| 型號: | ADV601LCJST |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 消費家電 |

| 英文描述: | Ultralow Cost Video Codec |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP120 |

| 封裝: | LQFP-120 |

| 文件頁數: | 23/52頁 |

| 文件大小: | 606K |

| 代理商: | ADV601LCJST |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當前第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

ADV601

–23–

REV. 0

Video Formats—CCIR-656

The ADV601 supports a glueless video interface to CCIR-656

devices when the Video Format is programmed to CCIR-656

mode. CCIR-656 requires that 4:2:2 data (8 or 10 bits per com-

ponent) be multiplexed and transmitted over a single 8- or 10-bit

physical interface. A 27 MHz clock is transmitted along with the

data. This clock is synchronous with the data. The color space of

CCIR-656 is YCrCb.

When in master mode, the CCIR-656 mode does not require

any external synchronization or blanking signals to accompany

digital video. Instead, CCIR-656 includes special time codes in

the stream syntax that define horizontal blanking periods, verti-

cal blanking periods, and field synchronization (horizontal and

vertical synchronization information can be derived). These

time codes are called End-of-Active-Video (EAV) and Start-of-

Active-Video (SAV). Each line of video has one EAV and one

SAV time code. EAV and SAV have three bits of embedded

information to define HSYNC, VSYNC and Field information

as well as error detection and correction bits.

VCLK is driven with a 27 MHz, 50% duty cycle clock which is

synchronous with the video data. Video data is clocked on the

rising edge of the VCLK signal. When decoding, the VCLK

signal is typically transmitted along with video data in the

CCIR-656 physical interface.

Electrically, CCIR-656 specifies differential ECL levels to be

used for all interfaces. The ADV601, however, only supports

unipolar, TTL logic thresholds. Systems designs that interface

to strictly conforming CCIR-656 devices (especially when inter-

facing over long cable distances) must include ECL level shifters

and line drivers.

The functionality of HSYNC, VSYNC and FIELD Pins is

dependent on three programmable modes of the ADV601:

Master-Slave Control, Encode-Decode Control and 525-625

Control. Table IX summarizes the functionality of these pins in

various modes.

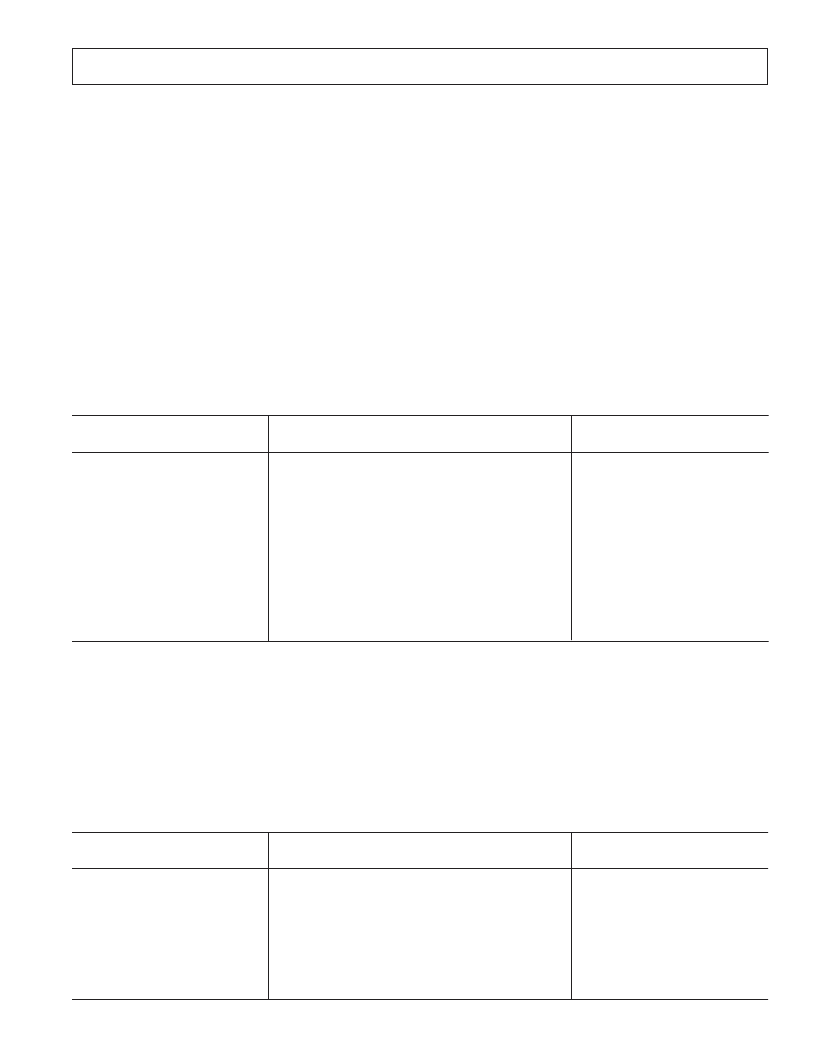

Table IX. CCIR-656 Master and Slave Modes HSYNC, VSYNC, and FIELD Functionality

HSYNC, VSYNC and FIELD

Functionality for CCIR-656

Master Mode (HSYNC, VSYNC

and FIELD Are Outputs)

Slave Mode (HSYNC, VSYNC

and FIELD Are Inputs)

Encode Mode (video data is input

to the chip)

Pins are driven to reflect the states of the

received time codes: EAV and SAV. This

functionality is independent of the state of

the 525-625 mode control. An encoder is

most likely to be in master mode.

Pins are output to the precise timing definitions

for CCIR-656 interfaces. The state of the pins

reflect the state of the EAV and SAV timing

codes that are generated in the output video data.

These definitions are different for 525 and 625 line

systems. The ADV601 completely manages the

generation and timing of these pins.

Undefined—Use Master Mode

Decode Mode (video data is output

from the chip)

Undefined—Use Master Mode

Video Formats—Philips Video

Philips video format requires 4:2:2 data (8 bits per component)

be transmitted over a two “lane” 16-bit physical interface. A

27 MHz clock is transmitted along with the data. This clock is

synchronous with the data and is running at twice the transfer

rate of the interface. The color space is YUV. VCLK is driven

with a 27 MHz 50% duty cycle clock, which is synchronous with

the video data. Philips video format requires external synchroni-

zation and blanking signals to accompany digital video. These

signals are VSYNC, HSYNC, CREF and FIELD. In general,

when the ADV601 is configured as an encoder, these signals will

all be inputs. When the ADV601 is configured as a decoder,

these signals will be outputs. There are special cases for this

described in Table X.

The functionality of HSYNC, VSYNC, and FIELD pins is depen-

dent on three programmable modes of the ADV601: Master-Slave

Control, Encode-Decode Control, and 525-625 Control. Table X

summarizes the functionality of these pins in various modes.

Table X. Philips Video Master and Slave Modes HSYNC, VSYNC and FIELD Functionality

HSYNC, VSYNC and FIELD

Functionality for Philips Video

Master Mode (HSYNC, VSYNC,

CREF and FIELD Are Outputs)

Slave Mode (HSYNC, VSYNC,

CREF and FIELD Are Inputs)

Encode Mode (video data is input

to the chip)

The ADV601 completely manages the generation

and timing of these pins. The device driving the

ADV601 video interface must use these outputs to

remain in sync with the ADV601. It is expected that

this combination of modes would not be used frequently.

The ADV601 completely manages the

generation and timing of these pins.

These pins are used to control the

blanking of video and sequencing

of the YSC, CSC, and LC counters.

Decode Mode (video data is output

from the chip)

These pins are used to control the

blanking of video and sequencing

of the YSC, CSC, and LC counters.

相關PDF資料 |

PDF描述 |

|---|---|

| ADV7120KP30 | CMOS 80 MHz, Triple 8-Bit Video DAC |

| ADV7120 | CMOS 80 MHz, Triple 8-Bit Video DAC |

| ADV7120KP50 | CMOS 80 MHz, Triple 8-Bit Video DAC |

| ADV7120KP80 | CMOS 80 MHz, Triple 8-Bit Video DAC |

| ADV7120KST30 | CMOS 80 MHz, Triple 8-Bit Video DAC |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADV601LCJSTRL | 制造商:Analog Devices 功能描述:Ultralow Cost Video Codec 120-Pin LQFP T/R |

| ADV601LCJSTZ | 功能描述:IC CODEC VIDEO DSP/SRL 120LQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 編解碼器 系列:- 標準包裝:2,500 系列:- 類型:立體聲音頻 數據接口:串行 分辨率(位):18 b ADC / DAC 數量:2 / 2 三角積分調變:是 S/N 比,標準 ADC / DAC (db):81.5 / 88 動態范圍,標準 ADC / DAC (db):82 / 87.5 電壓 - 電源,模擬:2.6 V ~ 3.3 V 電壓 - 電源,數字:1.7 V ~ 3.3 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:48-WFQFN 裸露焊盤 供應商設備封裝:48-TQFN-EP(7x7) 包裝:帶卷 (TR) |

| ADV601LCJSTZRL | 功能描述:IC CODEC VIDEO DSP/SRL 120LQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 編解碼器 系列:- 標準包裝:2,500 系列:- 類型:立體聲音頻 數據接口:串行 分辨率(位):18 b ADC / DAC 數量:2 / 2 三角積分調變:是 S/N 比,標準 ADC / DAC (db):81.5 / 88 動態范圍,標準 ADC / DAC (db):82 / 87.5 電壓 - 電源,模擬:2.6 V ~ 3.3 V 電壓 - 電源,數字:1.7 V ~ 3.3 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:48-WFQFN 裸露焊盤 供應商設備封裝:48-TQFN-EP(7x7) 包裝:帶卷 (TR) |

| ADV601LC-VIDEOPIPE | 制造商:Analog Devices 功能描述:TOOLS:DEVELOPMENT BOARDS H/W 制造商:Analog Devices 功能描述:EVALUATION BOARD ((NS)) |

| ADV601XS | 制造商:Analog Devices 功能描述: |

發布緊急采購,3分鐘左右您將得到回復。