- 您現在的位置:買賣IC網 > PDF目錄379669 > AN231E04 (Electronic Theatre Controls, Inc.) Dynamically Reconfigurable dpASP PDF資料下載

參數資料

| 型號: | AN231E04 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Dynamically Reconfigurable dpASP |

| 中文描述: | 動態可重構dpASP |

| 文件頁數: | 3/24頁 |

| 文件大小: | 445K |

| 代理商: | AN231E04 |

AN231E04 Datasheet – Dynamically Reconfigurable dpASP

DS231000-U001d

- 3 -

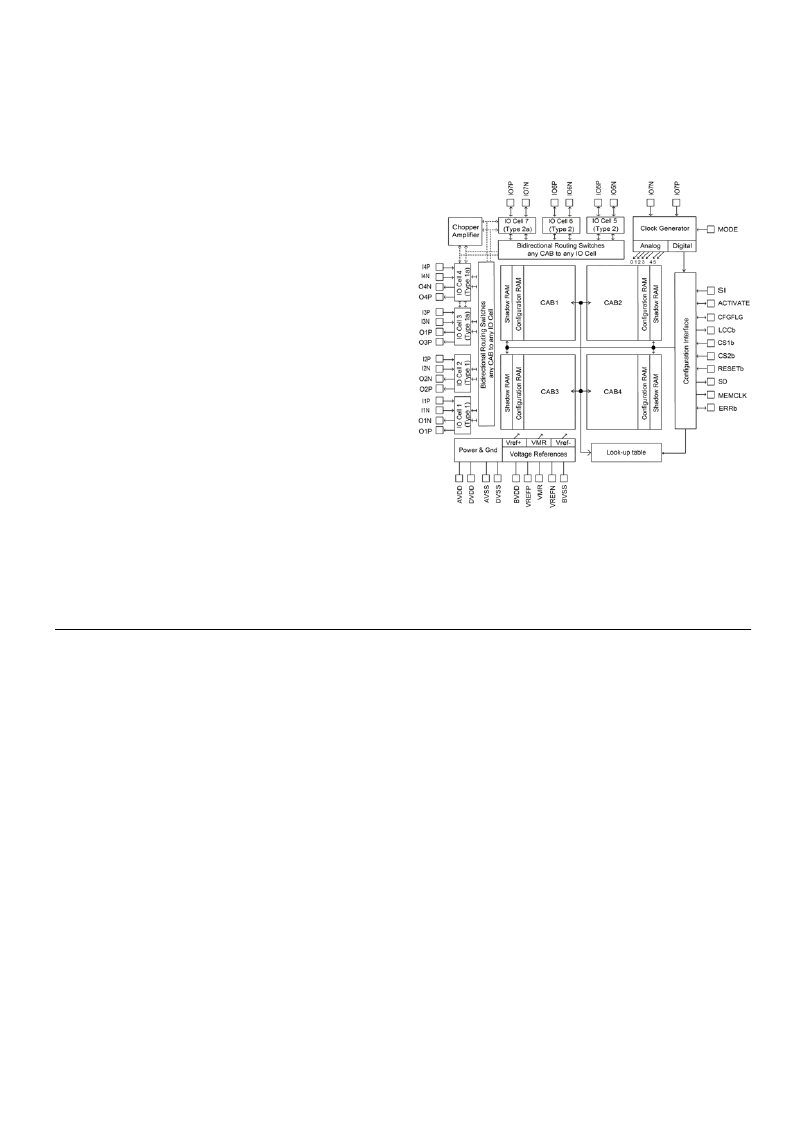

PRODUCT AND ARCHITECTURE OVERVIEW

The AN231E04 device is an “Analog Signal Processor”; ideally

suited to signal conditioning, filtering, gain, rectification, summing,

subtracting, multiplying, etc.

The device also accommodates nonlinear functions such as

sensor response linearization and arbitrary waveform synthesis.

The AN231E04 device consists of a 2x2 matrix of fully

Configurable

Analog

Blocks

programmable interconnect resources and analog input/output

cells with active elements. On chip clock generator block controls

multiple non-overlapping clock domains generated from an

external stable clock source. Internal band-gap reference

generator is used to create temperature compensated reference

voltage levels. The inclusion of an 8x256 bit look-up table

enables waveform synthesis and several non-linear functions.

Configuration data is stored in an on-chip SRAM configuration

memory. An SPI like interface is provided for simple serial load of

configuration data from a microprocessor or DSP. This memory is

shadowed allowing a different circuit configuration to be loaded

as a background task without disrupting the current circuit

functionality.

The AN231E04 device features seven configurable input/output

structures each can be used as input or output, 4 of the 7 have

integrated differential amplifiers. There is also a single chopper

stabilized amplifier that can be used by 3 of the 7 output cells.

Circuit design is enabled using Anadigmdesigner2 software, a

high level block diagram based circuitry entry tool. Circuit

functions are represented as CAMs (Configurable Analog

Modules) these are configurable block which map onto portions

of CABs. The software and a development board facilite instant

prototyping of any circuit captured in the tool.

PRODUCT FEATURES

Dynamic reconfiguration

Seven configurable I/O cells, two dedicated output cells

Fully differential architecture

I/O buffering with single ended to differential conversion

Low input offset through chopper stabilized amplifiers

256 Byte Look-Up Table (LUT) for linearization and

arbitrary signal generation

Typical Signal Bandwidth: DC-2MHz (Bandwidth is CAM

dependent)

Signal to Noise Ratio:

o

Broadband 90dB

o

Narrowband (audio) 120dB

Total Harmonic Distortion (THD): 100dB

User controlled Compensated low DC offset <250μV

DC Offset via chopper stabilized architecture <50uV

Package: 44-pin QFN (7x7x0.9mm)

o

Lead pitch 0.5mm

Supply voltage: 3.3V

ORDERING CODES

AN231E04-e2-QFNTY dpASP Tray (260 /tray, 2600/box)

AN231E04-e2-QFNTR dpASP Tape & Reel (1000 /reel, 4000/box)

(CABs),

surrounded

by

Figure 1: Architectural overview of the AN231E04 device

With dynamic reconfigurability, the functionality of the

AN231E04 can be reconfigured in-system by the designer or

on-the-fly by a microprocessor. A single AN231E04 can thus

be programmed to implement multiple analog functions

and/or to adapt on-the-fly to your circuit requirements.

APPLICATIONS

Analog Signal Processing

RFID IF (Baseband Filtering)

Real-time software control of analog system peripherals

Intelligent sensors

Adaptive filtering and control

Adaptive DSP front-end

Adaptive industrial control and automation

Self-calibrating systems

Compensation for aging of system components

Dynamic recalibration of remote systems

Ultra-low frequency signal conditioning

Custom analog signal processing

AN231E04-e2-QFNSP

AN231K04-DVLP3

dpASP Sample Pack

AN231E04 Development Kit

[

For more detailed information on the features of the AN231E04 device, please refer to the AN131E04/AN231E04 User Manual

]

相關PDF資料 |

PDF描述 |

|---|---|

| AN231E04-E2-QFNSP | Dynamically Reconfigurable dpASP |

| AN231E04-E2-QFNTR | Dynamically Reconfigurable dpASP |

| AN231E04-E2-QFNTY | Dynamically Reconfigurable dpASP |

| AN231K04-DVLP3 | Dynamically Reconfigurable dpASP |

| AN321 | AND / NOR circuit providing the logical function |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AN231E04-E2-QFNSP | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Dynamically Reconfigurable dpASP |

| AN231E04-E2-QFNTR | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Dynamically Reconfigurable dpASP |

| AN231E04-E2-QFNTY | 制造商:Anadigm 功能描述:Analog Signal Processor 44-Pin QFN EP Tray |

| AN231K04-DVLP3 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Dynamically Reconfigurable dpASP |

| AN232 | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:Low Frequency Magnetic Transmitter Design |

發布緊急采購,3分鐘左右您將得到回復。