- 您現在的位置:買賣IC網 > PDF目錄379669 > AN231K04-DVLP3 (Electronic Theatre Controls, Inc.) Dynamically Reconfigurable dpASP PDF資料下載

參數資料

| 型號: | AN231K04-DVLP3 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Dynamically Reconfigurable dpASP |

| 中文描述: | 動態可重構dpASP |

| 文件頁數: | 9/24頁 |

| 文件大小: | 445K |

| 代理商: | AN231K04-DVLP3 |

AN231E04 Datasheet – Dynamically Reconfigurable dpASP

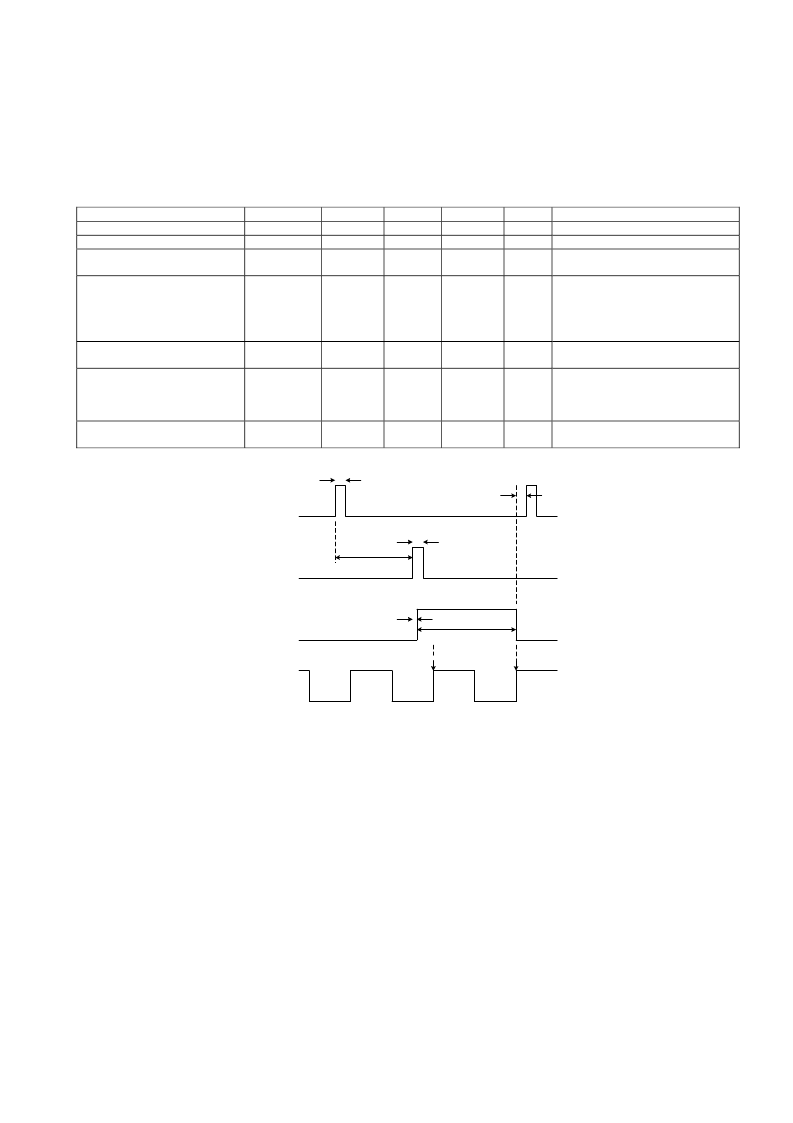

RAM Transfer – Trigger and Arm

These digital inputs do not have dedicated pins, a connection exists within the dpASP, an external signal can be routed to

either of these virtual pins from a type2 I/O cell (I/O cells 5, 6 and 7. Pins 15,16,17,18,19 or 20).

The purpose of these virtual pins is to extend optional asynchronous timing control of the dpASP configuration to the user.

DS231000-U001d

- 9 -

1.4.8

Parameter

Input Voltage Low

Input Voltage High

Minimum pulse width

connected to where

Pulse-Pulse edge delay

Symbol

Vil

Vih

T

PW

setup time

Min

0

70

Typ

Max

30

100

Unit

%

%

Comment

% of DVDD

% of DVDD

Time to register the event

internally.

Delay between pre-trigger and

trigger. Need not be observed if

pre-trigger is not used, is set at

the end of configuration

automatically.

Delay from trigger rising edge to

internal execute event.

Duration of execute pulse

guaranteed 1 ACLK period. Can

be as long as 2 periods

depending on relative phases.

Pre-trigger circuit is reset ready to

accept another pre-trigger.

5

-

-

ns

T

PT-T

setup time

10

-

-

ns

Execute delay

T

EXDLY

0

10

20

ns

Execute minimum width

T

MinEW

1 ALCK

-

2 ACLK

-

Pre-trigger reset.

T

PTR

10

-

-

ns

Pre-trigger

Trigger

ACLK

T

PW

T

PW

T

PT-T

T

MinEW

T

EXDLY

Internal

RAM

execute

T

PTR

edge (n)

edge (n+1)

AnadigmDesigner2 options, (these are set using the software tool AnadigmDesigner2)

RAM Transfer Trigger = Automatic

:

RAM transfer happens automatically immediately after the “end” byte of a configuration bit stream. Timing control is entirely inside the

AN231E04 device and not visible to a user.

RAM Transfer Trigger = Event driven

.

RAM Trigger = Off

.

no pre-trigger used. The “end” byte of configuration bit stream arms the RAM transfer and the user signal then acts

as the trigger.

Arm Trigger = On

External Signal Allowed = Trigger

. This setting allows the external signal connected to be the trigger,

Arming must be from an internal signal.

External Signal Allowed = Arm

. This setting allows the external signal connected to be the arming signal,

Trigger be from an internal signal.

RAM Transfer Trigger = Clock synch

RAM transfer happens automatically immediately following the first occurrence of all internal clocks being scyncronous. Timing control is

entirely inside the AN231E04 device and not visible to a user.

HINT: The RAM transfer timings above are for the trigger block hardware - The

Trigger

and

Arm

signals can come from many

sources, propagation delays to the trigger block inputs will vary depending on the source and routing of the signals to this block.

相關PDF資料 |

PDF描述 |

|---|---|

| AN321 | AND / NOR circuit providing the logical function |

| AN3791 | VTR X-VALUE SHIFT CIRCUIT |

| AN53 | The CS5322 Digital Filter |

| AN7203 | FM FRONT-END IC FOR RADIO, RADIO CASSETTE RECORDER |

| AN80T05LF | AN80T05LF (IC901) : REGULATOR |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AN232 | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:Low Frequency Magnetic Transmitter Design |

| AN2320S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Video Camera Circuit |

| AN23-23A | 制造商:AN# - MILITARY 功能描述: |

| AN23-25A | 制造商:AN# - MILITARY 功能描述: |

| AN232ISO | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:simple and effective protection against all surges, static electricity and ground loops in your RS232 line. |

發布緊急采購,3分鐘左右您將得到回復。