- 您現在的位置:買賣IC網 > PDF目錄379681 > AS6VA5128 (Electronic Theatre Controls, Inc.) 2.7V to 3.3V 512K X 8 Intelliwatt low-power CMOS SRAM PDF資料下載

參數資料

| 型號: | AS6VA5128 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 2.7V to 3.3V 512K X 8 Intelliwatt low-power CMOS SRAM |

| 中文描述: | 2.7V至3.3V為512k × 8 Intelliwatt低功耗CMOS SRAM的 |

| 文件頁數: | 2/9頁 |

| 文件大小: | 151K |

| 代理商: | AS6VA5128 |

2

ALLIANCE SEMICONDUCTOR

10/6/00

AS6VA5128

Functional description

The AS6VA5128 is a low-power CMOS 4,194,304-bit Static Random Access Memory (SRAM) device organized as

524,288 words × 8 bits. It is designed for memory applications where slow data access, low power, and simple interfacing

are desired.

Equal address access and cycle times (t

AA

, t

RC

, t

WC

) of 55 ns are ideal for low-power applications. Active high and low chip

selects (CS) permit easy memory expansion with multiple-bank memory systems.

When CS is high, the device enters standby mode: the AS6VA5128 is guaranteed not to exceed 66

μ

W power consumption

at 3.3V and 55ns. The device also returns data when V

CC

is reduced to 1.5V for even lower power consumption.

A write cycle is accomplished by asserting write enable (WE) and chip select (CS) low. Data on the input pins I/O1–I/O8 is

written on the rising edge of WE (write cycle 1) or CS (write cycle 2). To avoid bus contention, external devices should drive

I/O pins only after outputs have been disabled with output enable (OE) or write enable (WE).

A read cycle is accomplished by asserting output enable (OE), chip select (CS), with write enable (WE) High. The chip

drives I/O pins with the data word referenced by the input address. When either chip select or output enable is inactive, or

write enable is active, output drivers stay in high-impedance mode.

All chip inputs and outputs are CMOS-compatible, and operation is from a single 2.7V to 3.3V supply. The device is

available in the JEDEC standard 36(48)-ball FBGA package.

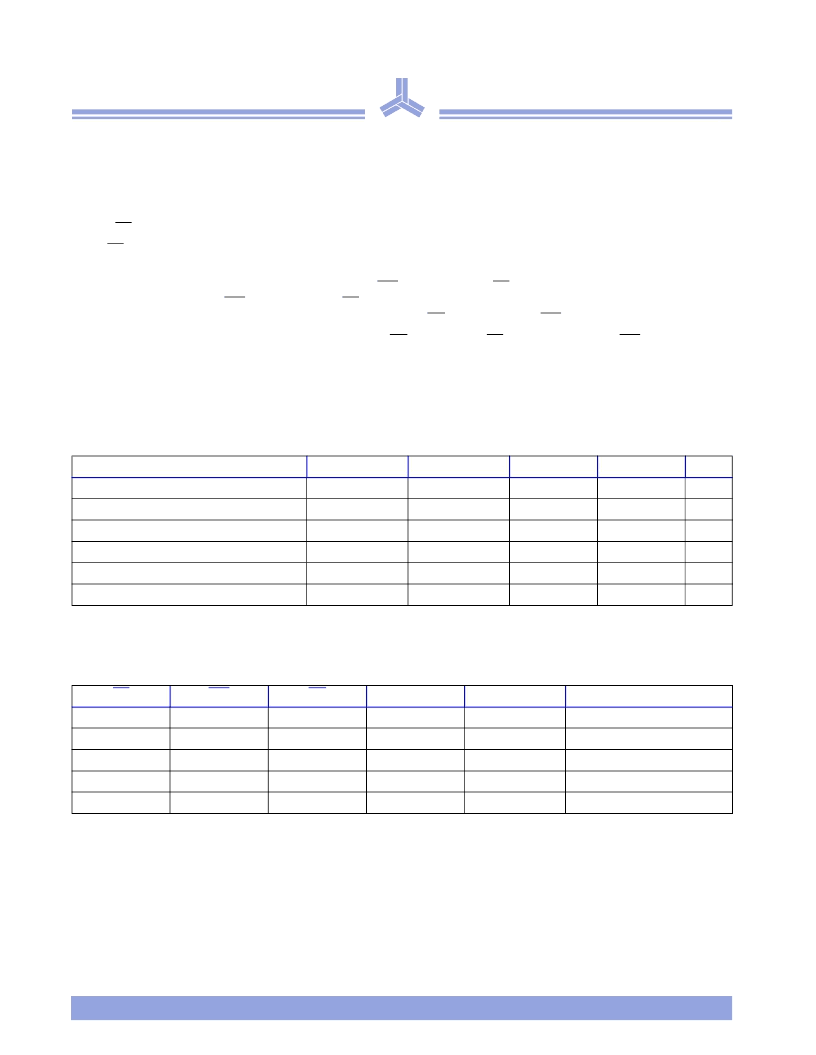

Absolute maximum ratings

Note: Stresses greater than those listed under

Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress rating only and

functional operation of the device at these or any other conditions outside those indicated in the operational sections of this specification is not implied.

Exposure to absolute maximum rating conditions for extended periods may affect reliability.

Truth table

Key: X = Don’t care, L = Low, H = High.

Parameter

Device

Symbol

Min

Max

Unit

Voltage on V

CC

relative to V

SS

Voltage on any I/O pin relative to GND

Power dissipation

V

tIN

V

tI/O

P

D

T

stg

T

bias

I

OUT

–0.5

V

CC

+ 0.5

V

–0.5

–

V

W

°

C

°

C

mA

1.0

Storage temperature (plastic)

–65

+150

Temperature with V

CC

applied

DC output current (low)

–55

–

+125

20

CS

WE

OE

Supply Current

I/O1–I/O8

Mode

H

L

X

X

X

X

I

SB

I

SB

I

CC

I

CC

I

CC

High Z

High Z

Standby (I

SB

)

Standby (I

SB

)

Output disable (I

CC

)

Read (I

CC

)

Write (I

CC

)

L

H

H

High Z

L

L

H

L

L

X

D

OUT

D

IN

相關PDF資料 |

PDF描述 |

|---|---|

| AS6VA5128-BC | 2.7V to 3.3V 512K X 8 Intelliwatt low-power CMOS SRAM |

| AS6VA5128-BI | 2.7V to 3.3V 512K X 8 Intelliwatt low-power CMOS SRAM |

| AS6VA5128 | 2.7V to 3.3V 512K × 8 Intelliwatt low-power CMOS SRAM(2.7V 到 3.3V 512K × 8 Intelliwatt 低功耗 CMOS 靜態RAM) |

| AS6WA25616 | 3.0V to 3.6V 256K?6 IntelliwattTM low-power CMOS SRAM with one chip enable |

| AS6WA25616-BI | 3.0V to 3.6V 256K?6 IntelliwattTM low-power CMOS SRAM with one chip enable |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AS6VA5128-BC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:2.7V to 3.3V 512K X 8 Intelliwatt low-power CMOS SRAM |

| AS6VA5128-BI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:2.7V to 3.3V 512K X 8 Intelliwatt low-power CMOS SRAM |

| AS6WA25616 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:3.0V to 3.6V 256K?6 IntelliwattTM low-power CMOS SRAM with one chip enable |

| AS6WA25616-BC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:3.0V to 3.6V 256K?6 IntelliwattTM low-power CMOS SRAM with one chip enable |

| AS6WA25616-BI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:3.0V to 3.6V 256K?6 IntelliwattTM low-power CMOS SRAM with one chip enable |

發布緊急采購,3分鐘左右您將得到回復。