- 您現在的位置:買賣IC網 > PDF目錄384209 > CL7192EQI160-20 PDF資料下載

參數資料

| 型號: | CL7192EQI160-20 |

| 文件頁數: | 1/16頁 |

| 文件大小: | 183K |

| 代理商: | CL7192EQI160-20 |

December 2000

Page 1

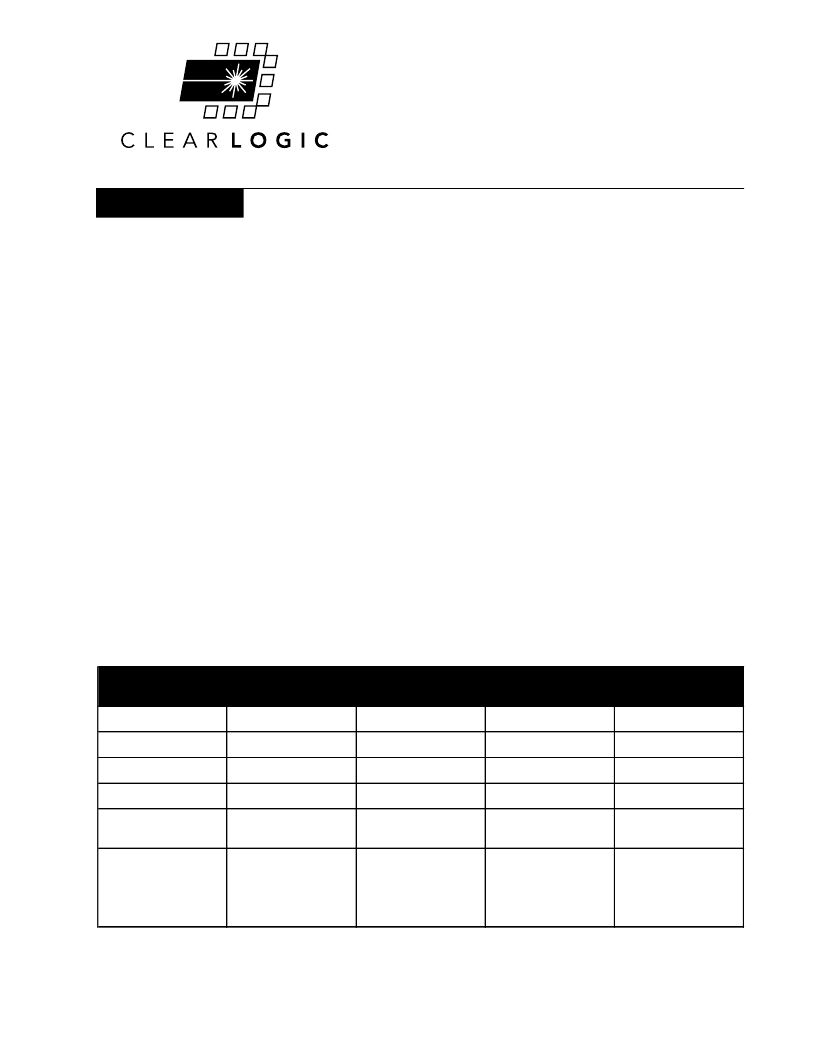

CL7128E

CL7128S

CL7160E

CL7160S

CL7192E

CL7192S

CL7256E

CL7256S

Useable Gates

2,500

3,200

3,750

5,000

Macrocells

128

160

192

256

Logic Blocks

8

10

12

16

Max user I/O pins

100

104

124

164

-5, -6, -7, -10,

-12, -15, -20

-5, -6, -7, -10,

-12, -15, -20

-6, -7, -10,

-12, -15, -20

-6, -7, -10,

-12, -15, -20

84-pin PLCC

100-pin TQFP

84-pin PLCC

100-pin TQFP

160-pin PQFP

160-pin PQFP

208-pin PQFP

100-pin PQFP

160-pin PQFP

100-pin PQFP

160-pin PQFP

208-pin RQFP

7K tbl 01B

Parameter

Packages

Speed Grades

u

Laser Processed Logic Device (LPLD) technology offers

the ultimate combination of performance, flexibility, and

low cost

u

Functionally, architecturally, and electrically compatible

with industry-standard Altera

MAX

7000

u

High Density

-

3,700 Usable gates

-

192 Macrocells

-

152 Maximum user I/O pins

u

Laser fuse technology provides very fast, dense

interconnect routing

u

Low current consumption

u

Supports 3.3 volt or 5.0 volt I/O operation

u

Alpha particle immune

CL7000 Product Family Overview

CL7192E

CL7192S

Laser Processed Logic Device Family

Key Features

相關PDF資料 |

PDF描述 |

|---|---|

| CL7192SQC160-10 | |

| CL7192SQC160-15 | Laser-Programmable Complex PLD |

| CL7192SQC160-7 | |

| CL7256AEFC100-10 | Electrically-Erasable Complex PLD |

| CL7256AEQC208-6 | |

相關代理商/技術參數 |

參數描述 |

|---|---|

| CL72001X | 制造商:BANDRIDGE 功能描述:LEAD AV CAT5 0.5M |

| CL72002X | 制造商:BANDRIDGE 功能描述:LEAD AV CAT5 2M |

| CL72003X | 制造商:BANDRIDGE 功能描述:LEAD AV CAT5 3M |

| CL72008X | 制造商:BANDRIDGE 功能描述:LEAD AV CAT5 7.5M |

| CL72015X | 制造商:BANDRIDGE 功能描述:LEAD AV CAT5 15M |

發布緊急采購,3分鐘左右您將得到回復。