- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄19024 > DC1620A-J (Linear Technology)BOARD DEMO 65MSPS LTC2142-14 PDF資料下載

參數(shù)資料

| 型號(hào): | DC1620A-J |

| 廠商: | Linear Technology |

| 文件頁數(shù): | 16/38頁 |

| 文件大小: | 0K |

| 描述: | BOARD DEMO 65MSPS LTC2142-14 |

| 軟件下載: | QuikEval II System |

| 設(shè)計(jì)資源: | DC1620A Design Files DC1620A Schematic |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | * |

| 相關(guān)產(chǎn)品: | DC890B-ND - BOARD USB DATA COLLECTION |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當(dāng)前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁

23

21421014fa

LTC2142-14/

LTC2141-14/LTC2140-14

50Ω

100Ω

0.1μF

T1 = MA/COM ETC1-1-13

RESISTORS AND CAPACITORS

ARE 0402 PACKAGE SIZE

50Ω

LTC2142

21421014 F12

ENC–

ENC+

0.1μF

T1

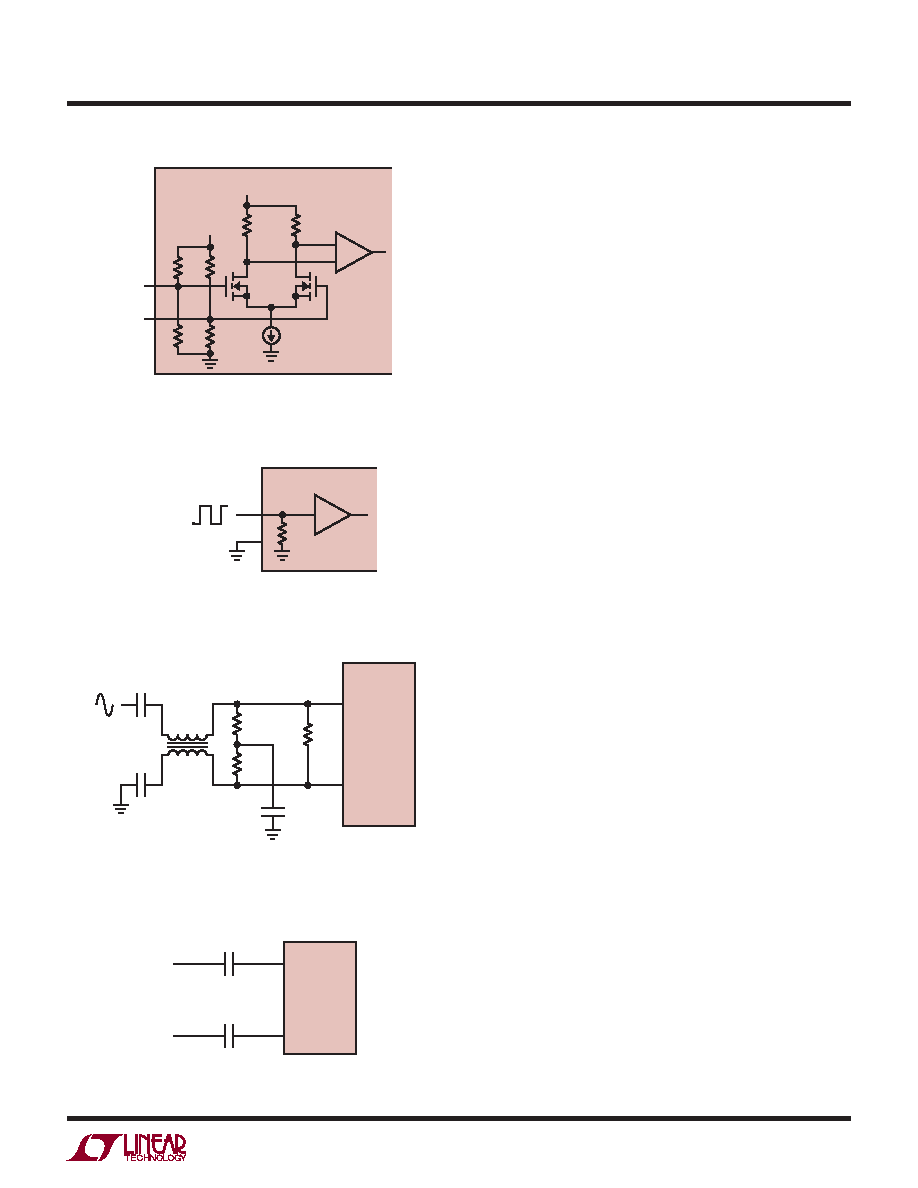

Figure 12. Sinusoidal Encode Drive

ENC+

ENC–

PECL OR

LVDS

CLOCK

0.1μF

21421014 F13

LTC2142

Figure 13. PECL or LVDS Encode Drive

VDD

LTC2142

21421014 F10

ENC–

ENC+

15k

VDD

DIFFERENTIAL

COMPARATOR

30k

Figure 10. Equivalent Encode Input Circuit

for Differential Encode Mode

30k

ENC+

ENC–

21421014 F11

0V

1.8V TO 3.3V

LTC2142

CMOS LOGIC

BUFFER

Figure 11. Equivalent Encode Input Circuit

for Single-Ended Encode Mode

ENC– should stay at least 200mV above ground to avoid

falsely triggering the single ended encode mode. For good

jitter performance ENC+ and ENC– should have fast rise

and fall times.

The single-ended encode mode should be used with CMOS

encode inputs. To select this mode, ENC– is connected

to ground and ENC+ is driven with a square wave encode

input. ENC+ can be taken above VDD (up to 3.6V) so 1.8V

to 3.3V CMOS logic levels can be used. The ENC+ threshold

is 0.9V. For good jitter performance, ENC+ should have

fast rise and fall times.

If the encode signal is turned off or drops below approxi-

mately 500kHz, the A/D enters nap mode.

Clock Duty Cycle Stabilizer

For good performance the encode signal should have a

50% (±5%) duty cycle. If the optional clock duty cycle

stabilizer circuit is enabled, the encode duty cycle can

vary from 30% to 70% and the duty cycle stabilizer will

maintain a constant 50% internal duty cycle. If the encode

signal changes frequency, the duty cycle stabilizer circuit

requires one hundred clock cycles to lock onto the input

clock. The duty cycle stabilizer is enabled by mode control

register A2 (serial programming mode), or by CS (parallel

programming mode).

For applications where the sample rate needs to be changed

quickly, the clock duty cycle stabilizer can be disabled. If

the duty cycle stabilizer is disabled, care should be taken to

make the sampling clock have a 50% (±5%) duty cycle. The

duty cycle stabilizer should not be used below 5Msps.

DIGITAL OUTPUTS

Digital Output Modes

The LTC2142-14/LTC2141-14/LTC2140-14 can operate in

three digital output modes: full rate CMOS, double data

rate CMOS (to halve the number of output lines), or double

data rate LVDS (to reduce digital noise in the system.) The

output mode is set by mode control register A3 (serial

programming mode), or by SCK (parallel programming

mode). Note that double data rate CMOS cannot be selected

in the parallel programming mode.

APPLICATIONS INFORMATION

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 1850 | LAMP T3-1/4 MINI BAYONET BASE |

| 89 | LAMP INCAND G-6 S.C. BAYONET |

| CL-927-ELP30-PC | CHROMALIT ELLIPSE LHT SRCE BULB |

| 521-0756 | LED T3 1/4 MINI PANEL BAYO 14V |

| BSO301SP H | MOSFET P-CH 30V 12.6A 8DSO |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DC1620A-K | 功能描述:BOARD DEMO 40MSPS LTC2141-14 RoHS:是 類別:未定義的類別 >> 其它 系列:* 標(biāo)準(zhǔn)包裝:1 系列:* 其它名稱:MS305720A |

| DC1620A-L | 功能描述:BOARD DEMO 25MSPS LTC2140-14 RoHS:是 類別:未定義的類別 >> 其它 系列:* 標(biāo)準(zhǔn)包裝:1 系列:* 其它名稱:MS305720A |

| DC1620A-M | 功能描述:BOARD DEMO 125MSPS LTC2145-12 RoHS:是 類別:未定義的類別 >> 其它 系列:* 標(biāo)準(zhǔn)包裝:1 系列:* 其它名稱:MS305720A |

| DC1620A-N | 功能描述:BOARD DEMO 105MSPS LTC2144-12 RoHS:是 類別:未定義的類別 >> 其它 系列:* 標(biāo)準(zhǔn)包裝:1 系列:* 其它名稱:MS305720A |

| DC1620A-O | 功能描述:BOARD DEMO 80MSPS LTC2143-12 RoHS:是 類別:未定義的類別 >> 其它 系列:* 標(biāo)準(zhǔn)包裝:1 系列:* 其它名稱:MS305720A |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。