- 您現在的位置:買賣IC網 > PDF目錄376726 > DJIXF972MNEA4 (Intel Corp.) Single-Port 10/100 Mbps PHY Transceiver PDF資料下載

參數資料

| 型號: | DJIXF972MNEA4 |

| 廠商: | Intel Corp. |

| 英文描述: | Single-Port 10/100 Mbps PHY Transceiver |

| 中文描述: | 單端口10/100 Mbps的物理層收發器 |

| 文件頁數: | 16/92頁 |

| 文件大小: | 666K |

| 代理商: | DJIXF972MNEA4 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁

Intel

LXT972M Single-Port 10/100 Mbps PHY Transceiver

16

Datasheet

Document Number: 302875-005

Revision Date: 27-Oct-2005

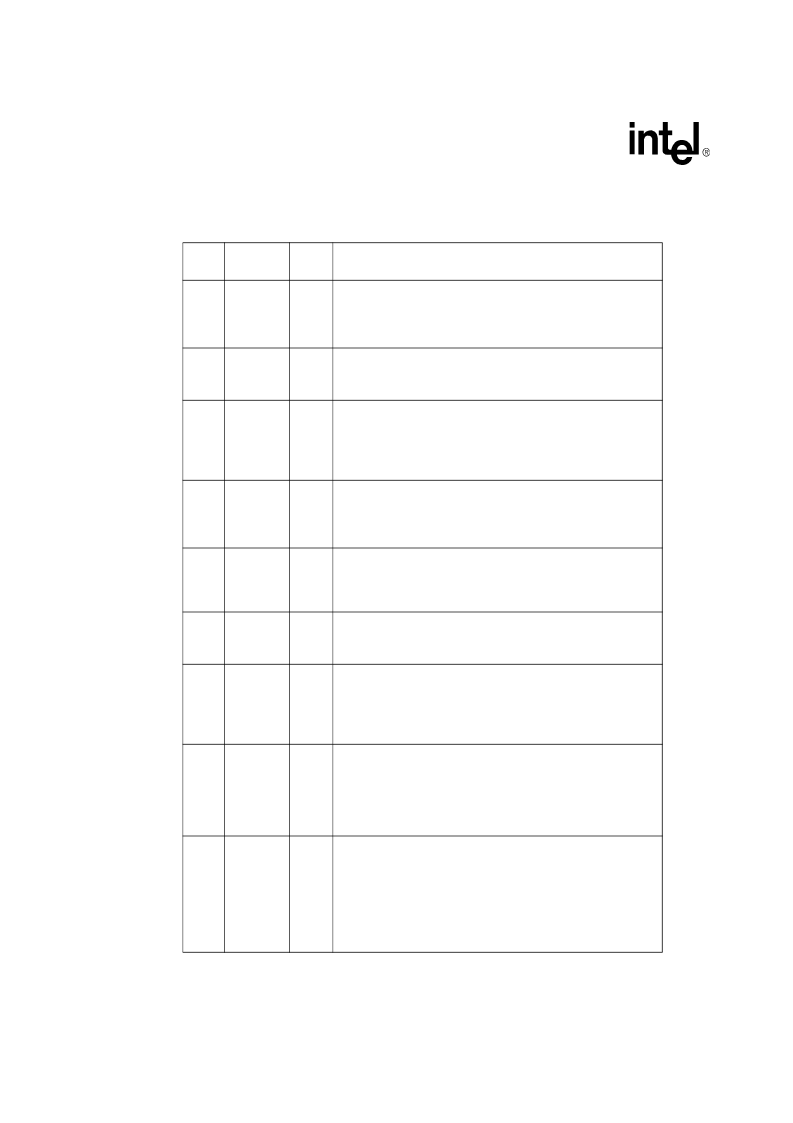

Table 4

lists signal descriptions of the LXT972M Transceiver MII data interface pins.

Table 4. Intel

LXT972M Transceiver MII Data Interface Signal Descriptions

LQFP

Pin#

Symbol

Type

Signal Description

47

46

45

44

TXD3

TXD2

TXD1

TXD0

I

Transmit Data.

TXD is a group of parallel data signals that are driven by the MAC.

TXD[3:0] transition synchronously with respect to TX_CLK.

TXD[0] is the least-significant bit.

43

TX_EN

I

Transmit Enable.

The MAC asserts this signal when it drives valid data on TXD.

This signal must be synchronized to TX_CLK.

42

TX_CLK

O

Transmit Clock.

TX_CLK is sourced by the PHY in both 10 and 100 Mbps

operations.

2.5 MHz for 10 Mbps operation

25 MHz for 100 Mbps operation.

33

34

35

36

RXD3

RXD2

RXD1

RXD0

O

Receive Data.

RXD is a group

of parallel signals that transition synchronously with

respect to RX_CLK.

RXD[0] is the least-significant bit.

37

RX_DV

O

Receive Data Valid.

The LXT972M Transceiver asserts this signal when it drives valid

data on RXD.

This output is synchronous to RX_CLK.

41

RX_ER

O

Receive Error.

Signals a receive error condition has occurred.

This output is synchronous to RX_CLK.

40

RX_CLK

O

Receive Clock.

25 MHz for 100 Mbps operation.

2.5 MHz for 10 Mbps operation.

For details, see

“Clock Requirements” on page 28

in

Chapter 5.0,

“Functional Description”

.

48

COL

O

Collision Detected

.

The LXT972M Transceiver asserts this output when a collision is

detected.

This output remains High for the duration of the collision.

This signal is asynchronous and is inactive during full- duplex

operation.

1

CRS

O

Carrier Sense

.

During half-duplex operation (Register bit 0.8 = 0), the LXT972M

Transceiver asserts this output when either transmitting or receiving

data packets.

During full-duplex operation (Register bit 0.8 = 1), CRS is asserted

only during receive.

CRS assertion is asynchronous with respect to RX_CLK. CRS is

de-asserted on loss of carrier, synchronous to RX_CLK.

相關PDF資料 |

PDF描述 |

|---|---|

| DJIXF972MPAA4 | Single-Port 10/100 Mbps PHY Transceiver |

| DJIXF972MPCA4 | Single-Port 10/100 Mbps PHY Transceiver |

| DJIXF972MPEA4 | Single-Port 10/100 Mbps PHY Transceiver |

| DJIXF972MQAA4 | Single-Port 10/100 Mbps PHY Transceiver |

| DJIXF972MQCA4 | Single-Port 10/100 Mbps PHY Transceiver |

相關代理商/技術參數 |

參數描述 |

|---|---|

| DJIXF972MPAA4 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Single-Port 10/100 Mbps PHY Transceiver |

| DJIXF972MPCA4 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Single-Port 10/100 Mbps PHY Transceiver |

| DJIXF972MPEA4 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Single-Port 10/100 Mbps PHY Transceiver |

| DJIXF972MQAA4 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Single-Port 10/100 Mbps PHY Transceiver |

| DJIXF972MQCA4 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Single-Port 10/100 Mbps PHY Transceiver |

發布緊急采購,3分鐘左右您將得到回復。