- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376798 > DM74S373N (FAIRCHILD SEMICONDUCTOR CORP) 3-STATE Octal D-Type Transparent Latches PDF資料下載

參數(shù)資料

| 型號(hào): | DM74S373N |

| 廠商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分類: | 通用總線功能 |

| 英文描述: | 3-STATE Octal D-Type Transparent Latches |

| 中文描述: | S SERIES, 8-BIT DRIVER, TRUE OUTPUT, PDIP20 |

| 封裝: | 0.300 INCH, PLASTIC, MS-001, DIP-20 |

| 文件頁(yè)數(shù): | 1/7頁(yè) |

| 文件大小: | 72K |

| 代理商: | DM74S373N |

2000 Fairchild Semiconductor Corporation

DS006486

www.fairchildsemi.com

August 1986

Revised May 2000

D

DM74S373

DM74S374

3-STATE Octal D-Type Transparent Latches

and Edge-Triggered Flip-Flops

General Description

These 8-bit registers feature totem-pole 3-STATE outputs

designed specifically for driving highly-capacitive or rela-

tively low-impedance loads. The high-impedance state and

increased high-logic-level drive provide these registers with

the capability of being connected directly to and driving the

bus lines in a bus-organized system without need for inter-

face or pull-up components. They are particularly attractive

for implementing buffer registers, I/O ports, bidirectional

bus drivers, and working registers.

The eight latches of the DM74S373 are transparent D-type

latches meaning that while the enable (G) is HIGH the Q

outputs will follow the data (D) inputs. When the enable is

taken LOW the output will be latched at the level of the

data that was set up.

The eight flip-flops of the DM74S374 are edge-triggered D-

type flip-flops. On the positive transition of the clock, the Q

outputs will be set to the logic states that were set up at the

D inputs.

Schmitt-trigger buffered inputs at the enable/clock lines

simplify system design as ac and dc noise rejection is

improved by typically 400 mV due to the input hysteresis. A

buffered output control input can be used to place the eight

outputs in either a normal logic state (HIGH or LOW logic

levels) or a high-impedance state. In the high-impedance

state the outputs neither load nor drive the bus lines signifi-

cantly.

The output control does not affect the internal operation of

the latches or flip-flops. That is, the old data can be

retained or new data can be entered even while the outputs

are OFF.

Features

I

Choice of 8 latches or 8 D-type flip-flops in a single

package

I

3-STATE bus-driving outputs

I

Full parallel-access for loading

I

Buffered control inputs

I

P-N-P input reduce D-C loading on data lines

Ordering Code:

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

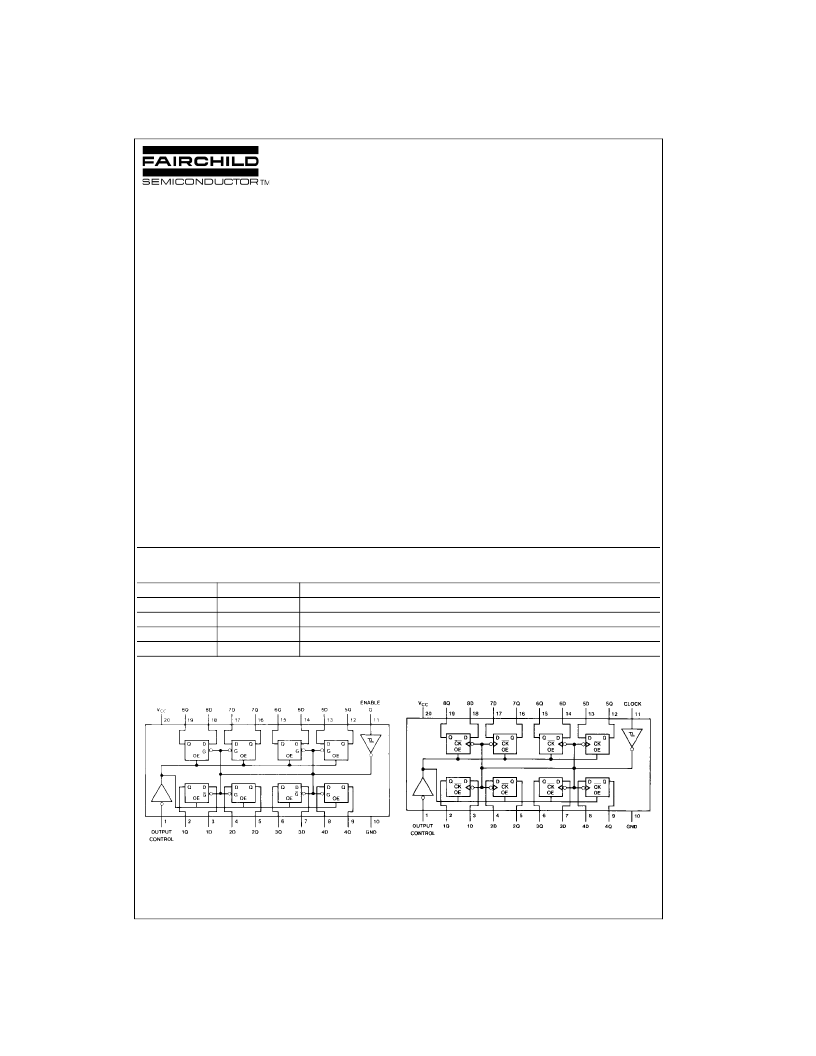

Connection Diagrams

DM74S373N

DM74S374N

Order Number

DM74S373WM

DM74S373N

DM74S374WM

DM74S374N

Package Number

M20B

N20A

M20B

N20A

Package Description

20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide

20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide

20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DM74S373WM | 3-STATE Octal D-Type Transparent Latches |

| DM74S374N | 3-STATE Octal D-Type Transparent Latches |

| DM74S374WM | 3-STATE Octal D-Type Transparent Latches |

| DM74S373WMX | 8-Bit D-Type Latch |

| DM74S374WMX | Octal D-Type Flip-Flop |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DM74S374 WAF | 制造商:Fairchild Semiconductor Corporation 功能描述: |

| DM74S374J | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Texas Instruments 功能描述: |

| DM74S374N | 功能描述:觸發(fā)器 3-STATE D Flip-Flop RoHS:否 制造商:Texas Instruments 電路數(shù)量:2 邏輯系列:SN74 邏輯類型:D-Type Flip-Flop 極性:Inverting, Non-Inverting 輸入類型:CMOS 輸出類型: 傳播延遲時(shí)間:4.4 ns 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:X2SON-8 封裝:Reel |

| DM74S381 WAF | 制造商:Fairchild Semiconductor Corporation 功能描述: |

| DM74S40 WAF | 制造商:Fairchild Semiconductor Corporation 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。