- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385317 > GS8170LW36C-333I (Electronic Theatre Controls, Inc.) 18Mb sigma 1x1Lp CMOS I/O Late Write SigmaRAM PDF資料下載

參數(shù)資料

| 型號(hào): | GS8170LW36C-333I |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 18Mb sigma 1x1Lp CMOS I/O Late Write SigmaRAM |

| 中文描述: | 35.7西格馬1x1Lp的CMOS的I / O后寫入SigmaRAM |

| 文件頁(yè)數(shù): | 4/27頁(yè) |

| 文件大小: | 884K |

| 代理商: | GS8170LW36C-333I |

第1頁(yè)第2頁(yè)第3頁(yè)當(dāng)前第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)

GS8170LW36/72C-333/300/250/200

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

Rev: 2.03 1/2005

4/27

2002, GSI Technology, Inc.

Operation Control

All address, data and control inputs (with the exception of EP2, EP3, ZQ, and the mode pins, L6, M6, and J6) are synchronized to

rising clock edges. Data in is captured on both rising and falling edges of CK. Read and write operations must be initiated with the

Advance/Load pin (ADV) held low, in order to load the new address. Device activation is accomplished by asserting all three of

the Chip Enable inputs (E1, E2, and E3). Deassertion of any one of the Enable inputs will deactivate the device.

It should be noted

that ONLY deactivation of the RAM via E2 and/or E3 deactivates the Echo Clocks, CQ1–CQ2.

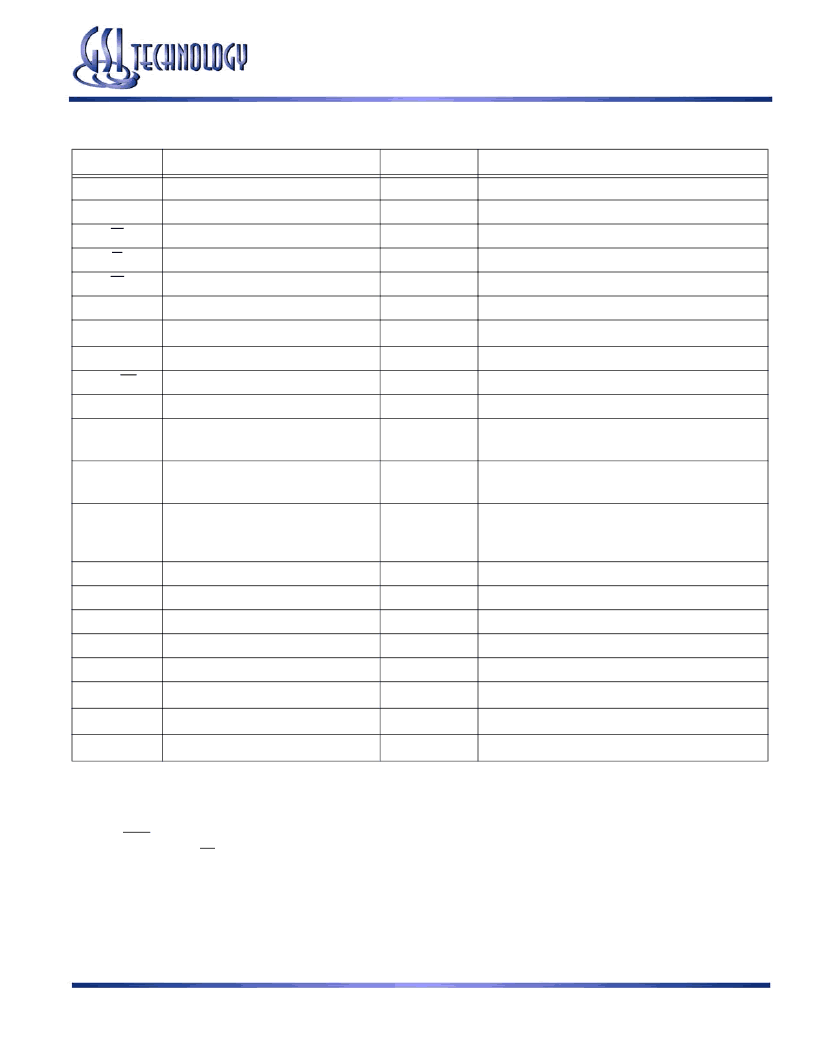

Pin Description Table

Symbol

Description

Type

Comments

A

Address

Input

—

ADV

Advance

Input

Active High

Bx

Byte Write Enable

Input

Active Low

W

Write Enable

Input

Active Low

E1

Chip Enable

Input

Active Low

E2 & E3

Chip Enable

Input

Programmable Active High or Low

EP2 & EP3

Chip Enable Program Pin

Mode Input

To be tied directly to V

DD

, V

DDQ

or V

SS

CK

Clock

Input

Active High

CQ, CQ

Echo Clock

Output

Three State - Deselect via E2 or E3 False

DQ

Data I/O

Input/Output

Three State

MCH

Must Connect High

Input

Active High

To be tied directly to V

DD

or V

DDQ

MCL

Must Connect Low

Input

Active Low

To be tied directly to V

SS

ZQ

Output Impedance Control

Mode Input

Low = Low Impedance [High Drive]

High = High Impedance [Low Drive]

To be tied directly to V

DDQ

or V

SS

TCK

Test Clock

Input

Active High

TDI

Test Data In

Input

—

TDO

Test Data Out

Output

—

TMS

Test Mode Select

Input

—

NC

No Connect

—

Not connected to die or any other pin

V

DD

Core Power Supply

Input

1.8 V Nominal

V

DDQ

Output Driver Power Supply

Input

1.8 V Nominal

V

SS

Ground

Input

—

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GS8170LW36 | Low-Noise Operational Amplifier 8-PDIP -40 to 85 |

| GS8170LW36C-200 | Low-Noise Operational Amplifier 8-PDIP -40 to 85 |

| GS8170LW36C-200I | Low-Noise Operational Amplifier 8-SO -40 to 85 |

| GS8170LW36C-250 | Low-Noise Operational Amplifier 8-SO -40 to 85 |

| GS8170LW36C-250I | Low-Noise Operational Amplifier 8-SO -40 to 85 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GS8170LW72AC-300I | 制造商:GSI Technology 功能描述:SRAM SYNC OCTAL 1.8V 18MBIT 256KX72 1.8NS 209FBGA - Trays |

| GS8170LW72AC-350 | 制造商:GSI Technology 功能描述:SRAM SYNC OCTAL 1.8V 18MBIT 256KX72 1.7NS 209FBGA - Trays |

| GS8170LW72AGC-250 | 制造商:GSI Technology 功能描述:SRAM SYNC OCTAL 1.8V 18MBIT 256KX72 2.1NS 209FBGA - Trays |

| GS8170LW72AGC-300 | 制造商:GSI Technology 功能描述:SRAM SYNC OCTAL 1.8V 18MBIT 256KX72 1.8NS 209FBGA - Trays |

| GS8170LW72AGC-333 | 制造商:GSI Technology 功能描述:SRAM SYNC OCTAL 1.8V 18MBIT 256KX72 1.8NS 209FBGA - Trays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。