- 您現在的位置:買賣IC網 > PDF目錄385317 > GS8170LW72C-200 (Electronic Theatre Controls, Inc.) Low-Noise Operational Amplifier 8-SOIC -40 to 85 PDF資料下載

參數資料

| 型號: | GS8170LW72C-200 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Low-Noise Operational Amplifier 8-SOIC -40 to 85 |

| 中文描述: | 35.7西格馬1x1Lp的CMOS的I / O后寫入SigmaRAM |

| 文件頁數: | 8/27頁 |

| 文件大小: | 884K |

| 代理商: | GS8170LW72C-200 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁

GS8170LW36/72C-333/300/250/200

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

Rev: 2.03 1/2005

8/27

2002, GSI Technology, Inc.

Burst Order

The burst address counter wraps around to its initial state after four internal addresses (the loaded address and three more) have

been accessed. SigmaRAMs always count in linear burst order.

Note:

The burst counter wraps to initial state on the 5th rising edge of clock.

Echo Clock

Σ

RAMs feature Echo Clocks, CQ1, CQ2, CQ1, and CQ2 that track the performance of the output drivers. The Echo Clocks are

delayed copies of the main RAM clock, CK. Echo Clocks are designed to track changes in output driver delays due to variance in

die temperature and supply voltage. The Echo Clocks are designed to fire with the rest of the data output drivers. SigmaRAMs

provide both in-phase, or true, Echo Clock outputs (CQ1 and CQ2) and inverted Echo Clock outputs (CQ1 and CQ2).

It should be noted that deselection of the RAM via E2 and E3 also deselects the Echo Clock output drivers. The deselection of

Echo Clock drivers is always pipelined to the same degree as output data.

Deselection of the RAM via E1 does not deactivate the

Echo Clocks.

Programmable Enables

Σ

RAMs feature two user-programmable chip enable inputs, E2 and E3. The sense of the inputs, whether they function as active

low or active high inputs, is determined by the state of the programming inputs, EP2 and EP3. For example, if EP2 is held at V

DD

,

E2 functions as an active high enable. If EP2 is held to V

SS

, E2 functions as an active low chip enable input.

Programmability of E2 and E3 allows four banks of depth expansion to be accomplished with no additional logic. By programming

the enable inputs of four SRAMs in binary sequence (00, 01, 10, 11) and driving the enable inputs with two address inputs, four

SRAMs can be made to look like one larger RAM to the system.

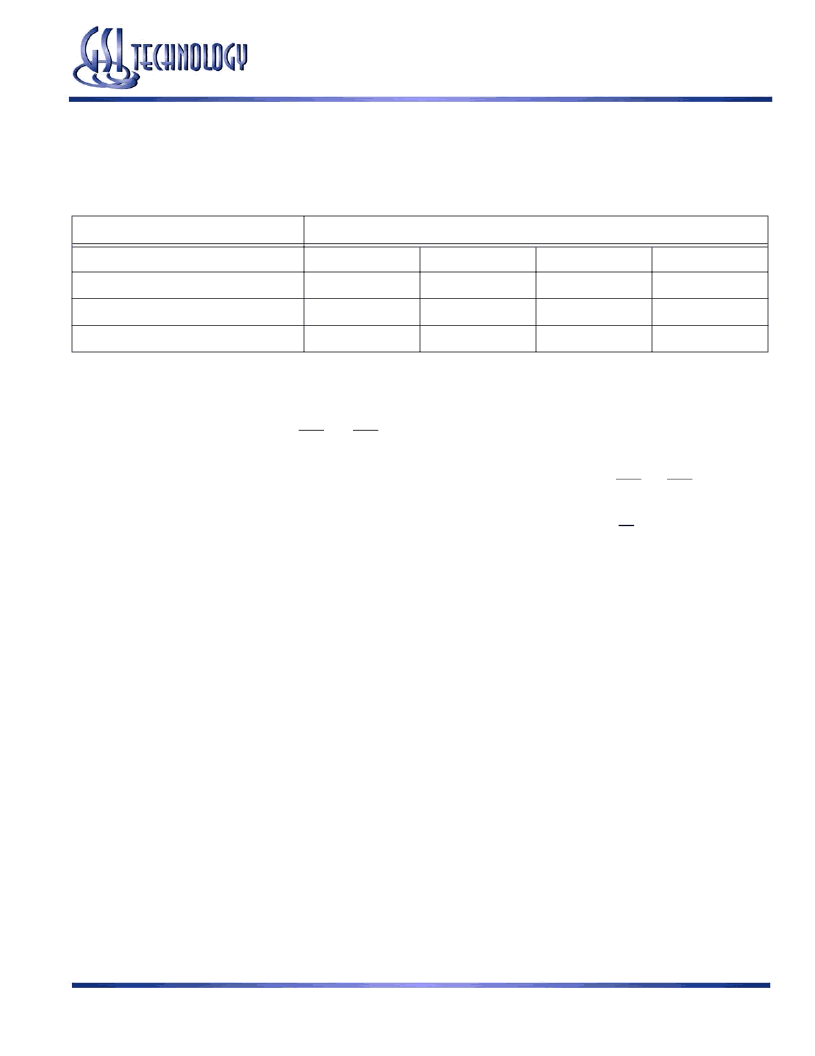

Linear Burst Order

A[1:0]

1st address

00

01

10

11

2nd address

01

10

11

00

3rd address

10

11

00

01

4th address

11

00

01

10

相關PDF資料 |

PDF描述 |

|---|---|

| GS8170LW72C-200I | Low-Noise Operational Amplifier 8-SOIC -40 to 85 |

| GS8170LW72C-250 | Low-Noise Operational Amplifier 8-SOIC -40 to 85 |

| GS8170LW72C-250I | Low-Noise Operational Amplifier 8-SOIC -40 to 85 |

| GS8170LW72C-300 | Low-Noise Operational Amplifier 8-SOIC -40 to 85 |

| GS8170LW72C-300I | Low-Noise Operational Amplifier 8-SOIC -40 to 85 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| GS8171DW36AC-300I | 制造商:GSI Technology 功能描述:SRAM SYNC QUAD 1.8V 18MBIT 512KX36 1.8NS 209FBGA - Trays |

| GS8171DW36AC-350 | 制造商:GSI Technology 功能描述:SRAM SYNC QUAD 1.8V 18MBIT 512KX36 1.7NS 209FBGA - Trays |

| GS8171DW36AC-350I | 制造商:GSI Technology 功能描述:SRAM SYNC QUAD 1.8V 18MBIT 512KX36 1.7NS 209BGA - Trays |

| GS8171DW36AGC-250 | 制造商:GSI Technology 功能描述:SRAM SYNC QUAD 1.8V 18MBIT 512KX36 2.1NS 209FBGA - Trays |

| GS8171DW36AGC-300 | 制造商:GSI Technology 功能描述:SRAM SYNC QUAD 1.8V 18MBIT 512KX36 1.8NS 209FBGA - Trays |

發布緊急采購,3分鐘左右您將得到回復。