- 您現在的位置:買賣IC網 > PDF目錄385317 > GS8170LW72C-333 (Electronic Theatre Controls, Inc.) Low-Noise Operational Amplifier 8-PDIP -40 to 85 PDF資料下載

參數資料

| 型號: | GS8170LW72C-333 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Low-Noise Operational Amplifier 8-PDIP -40 to 85 |

| 中文描述: | 35.7西格馬1x1Lp的CMOS的I / O后寫入SigmaRAM |

| 文件頁數: | 5/27頁 |

| 文件大小: | 884K |

| 代理商: | GS8170LW72C-333 |

第1頁第2頁第3頁第4頁當前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁

GS8170LW36/72C-333/300/250/200

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

Rev: 2.03 1/2005

5/27

2002, GSI Technology, Inc.

Read Operations

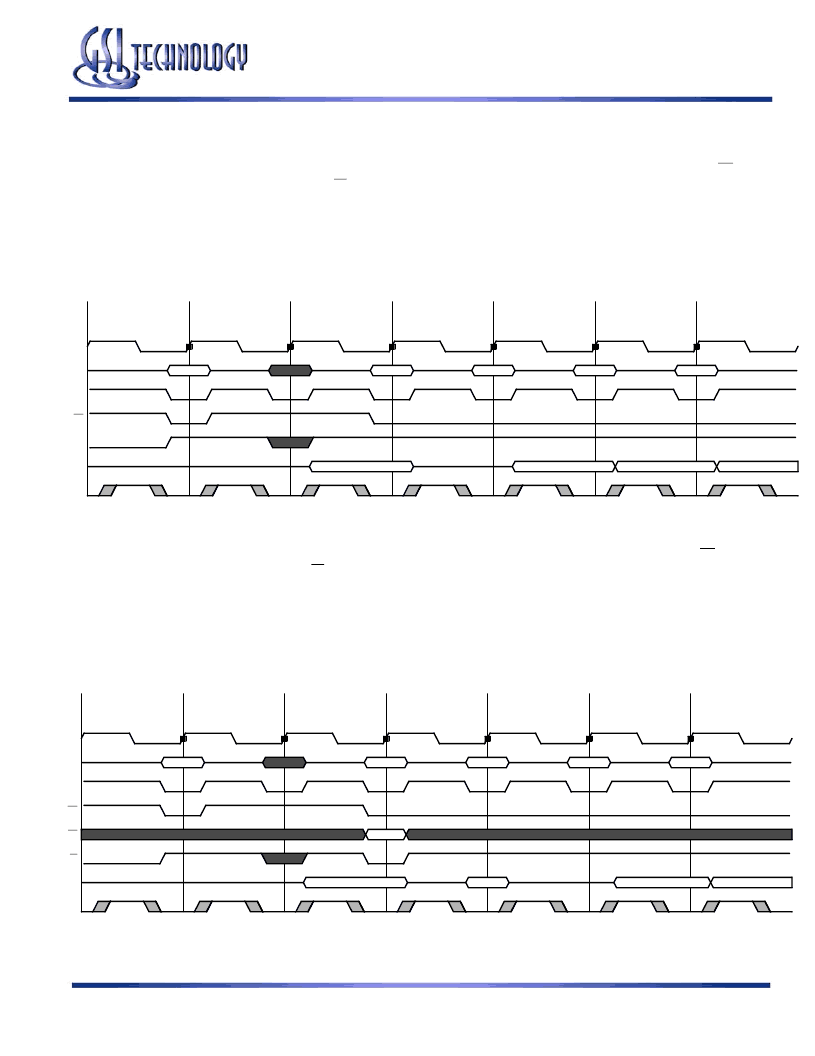

Pipelined Read

Read operation is initiated when the following conditions are satisfied at the rising edge of clock: All three chip enables (E1, E2,

and E3) are active, the write enable input signal (W) is deasserted high, and ADV is asserted low. The address presented to the

address inputs is latched into the address register and presented to the memory core and control logic. The control logic determines

that a read access is in progress and allows the requested data to propagate to the input of the output register. At the next rising edge

of clock the read data is allowed to propagate through the output register and onto the output pins

Single Data Rate (SDR) Pipelined Read.

Write Operations

Write operation occurs when the following conditions are satisfied at the rising edge of clock: All three chip enables (E1, E2, and

E3) are active, the write enable input signal (W) is asserted low, and ADV is asserted low.

Late Write

In Late Write mode the RAM requires Data In one rising clock edge later than the edge used to load Address and Control. Late

Write protocol has been employed on SRAMs designed for RISC processor L2 cache applications and in Flow Through mode NBT

SRAMs

SigmaRAM Late Write with Pipelined Read

Read A

Deselect

Read B

Read C

Read D

A

B

C

D

E

Q(A)

Q(B)

Q(C)

Q(D)

CK

Address

ADV

E1

W

DQ

CQ

Read A

Deselect

Write B

Read C

Read D

A

B

C

D

E

Q(A)

D(B)

Q(C)

Q(D)

CK

Address

ADV

E1

Bx

W

DQ

CQ

相關PDF資料 |

PDF描述 |

|---|---|

| GS832136GE-150IV | 2M x 18, 1M x 32, 1M x 36 36Mb Sync Burst SRAMs |

| GS832136E-200IV | 2M x 18, 1M x 32, 1M x 36 36Mb Sync Burst SRAMs |

| GS832136E-200V | 2M x 18, 1M x 32, 1M x 36 36Mb Sync Burst SRAMs |

| GS832136E-225IV | 2M x 18, 1M x 32, 1M x 36 36Mb Sync Burst SRAMs |

| GS832136E-225V | 2M x 18, 1M x 32, 1M x 36 36Mb Sync Burst SRAMs |

相關代理商/技術參數 |

參數描述 |

|---|---|

| GS8171DW36AC-300I | 制造商:GSI Technology 功能描述:SRAM SYNC QUAD 1.8V 18MBIT 512KX36 1.8NS 209FBGA - Trays |

| GS8171DW36AC-350 | 制造商:GSI Technology 功能描述:SRAM SYNC QUAD 1.8V 18MBIT 512KX36 1.7NS 209FBGA - Trays |

| GS8171DW36AC-350I | 制造商:GSI Technology 功能描述:SRAM SYNC QUAD 1.8V 18MBIT 512KX36 1.7NS 209BGA - Trays |

| GS8171DW36AGC-250 | 制造商:GSI Technology 功能描述:SRAM SYNC QUAD 1.8V 18MBIT 512KX36 2.1NS 209FBGA - Trays |

| GS8171DW36AGC-300 | 制造商:GSI Technology 功能描述:SRAM SYNC QUAD 1.8V 18MBIT 512KX36 1.8NS 209FBGA - Trays |

發布緊急采購,3分鐘左右您將得到回復。