- 您現在的位置:買賣IC網 > PDF目錄385338 > GS8662S08GE-167I (GSI TECHNOLOGY) 72Mb Burst of 2 DDR SigmaSIO-II SRAM PDF資料下載

參數資料

| 型號: | GS8662S08GE-167I |

| 廠商: | GSI TECHNOLOGY |

| 元件分類: | DRAM |

| 英文描述: | 72Mb Burst of 2 DDR SigmaSIO-II SRAM |

| 中文描述: | 8M X 8 DDR SRAM, 0.5 ns, PBGA165 |

| 封裝: | 15 X 17 MM, 1 MM PITCH, ROHS COMPLIANT, MO-216CAB-1, FPBGA-165 |

| 文件頁數: | 9/37頁 |

| 文件大小: | 960K |

| 代理商: | GS8662S08GE-167I |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

Preliminary

GS8662S08/09/18/36E-333/300/250/200/167

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

Rev: 1.01 9/2005

9/37

2005, GSI Technology

Special Functions

Byte Write and Nybble Write Control

Byte Write Enable pins are sampled at the same time that Data In is sampled. A high on the Byte Write Enable pin associated with

a particular byte (e.g., BW0 controls D0–D8 inputs) will inhibit the storage of that particular byte, leaving whatever data may be

stored at the current address at that byte location undisturbed. Any or all of the Byte Write Enable pins may be driven high or low

during the data in sample times in a write sequence.

Each write enable command and write address loaded into the RAM provides the base address for a 2 beat data transfer. The x18

version of the RAM, for example, may write 36 bits in association with each address loaded. Any 9-bit byte may be masked in any

write sequence.

Nybble Write (4-bit) control is implemented on the 8-bit-wide version of the device. For the x8 version of the device, “Nybble

Write Enable” and “NWx” may be substituted in all the discussion above.

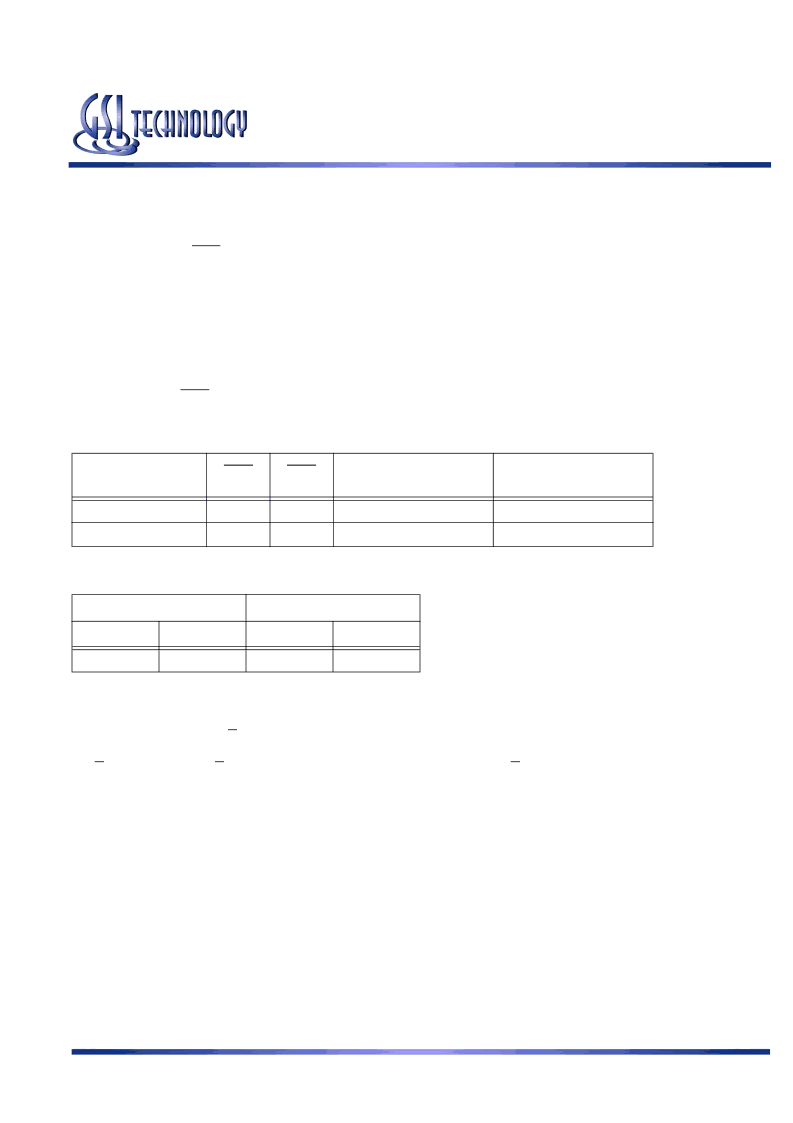

Example x18 RAM Write Sequence using Byte Write Enables

Data In Sample

Time

BW0

BW1

D0–D8

D9–D17

Beat 1

0

1

Data In

Don’t Care

Beat 2

1

0

Don’t Care

Data In

Resulting Write Operation

Beat 1

Beat 2

D0–D8

D9–D17

D0–D8

D9–D17

Written

Unchanged

Unchanged

Written

Output Register Control

SigmaSIO-II SRAMs offer two mechanisms for controlling the output data registers. Typically, control is handled by the Output

Register Clock inputs, C and C. The Output Register Clock inputs can be used to make small phase adjustments in the firing of the

output registers by allowing the user to delay driving data out as much as a few nanoseconds beyond the next rising edges of the K

and K clocks. If the C and C clock inputs are tied high, the RAM reverts to K and K control of the outputs.

相關PDF資料 |

PDF描述 |

|---|---|

| GS8662S08GE-200 | 72Mb Burst of 2 DDR SigmaSIO-II SRAM |

| GS8662S08GE-200I | 72Mb Burst of 2 DDR SigmaSIO-II SRAM |

| GS8662S08GE-250 | 72Mb Burst of 2 DDR SigmaSIO-II SRAM |

| GS8662S08GE-250I | 72Mb Burst of 2 DDR SigmaSIO-II SRAM |

| GS8662S08GE-300 | 72Mb Burst of 2 DDR SigmaSIO-II SRAM |

相關代理商/技術參數 |

參數描述 |

|---|---|

| GS8662S08GE-200 | 制造商:GSI 制造商全稱:GSI Technology 功能描述:72Mb Burst of 2 DDR SigmaSIO-II SRAM |

| GS8662S08GE-200I | 制造商:GSI 制造商全稱:GSI Technology 功能描述:72Mb Burst of 2 DDR SigmaSIO-II SRAM |

| GS8662S08GE-250 | 制造商:GSI 制造商全稱:GSI Technology 功能描述:72Mb Burst of 2 DDR SigmaSIO-II SRAM |

| GS8662S08GE-250I | 制造商:GSI 制造商全稱:GSI Technology 功能描述:72Mb Burst of 2 DDR SigmaSIO-II SRAM |

| GS8662S08GE-300 | 制造商:GSI 制造商全稱:GSI Technology 功能描述:72Mb Burst of 2 DDR SigmaSIO-II SRAM |

發布緊急采購,3分鐘左右您將得到回復。