- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385404 > HT82V24 (Holtek Semiconductor Inc.) 16-Bit, 15MSPS, 3-Channel CCD/CIS Analog Signal Processor PDF資料下載

參數(shù)資料

| 型號: | HT82V24 |

| 廠商: | Holtek Semiconductor Inc. |

| 英文描述: | 16-Bit, 15MSPS, 3-Channel CCD/CIS Analog Signal Processor |

| 中文描述: | 16位,15MSPS,3通道防治荒漠化公約/獨(dú)聯(lián)體模擬信號處理器 |

| 文件頁數(shù): | 7/21頁 |

| 文件大小: | 216K |

| 代理商: | HT82V24 |

HT82V24

Rev. 1.00

7

September 7, 2005

-

6

7

8 8 !

9

8 8 !

)

'

%

0 :

&

-

6

7

;

9

;

/

/

)

'

%

0 :

2

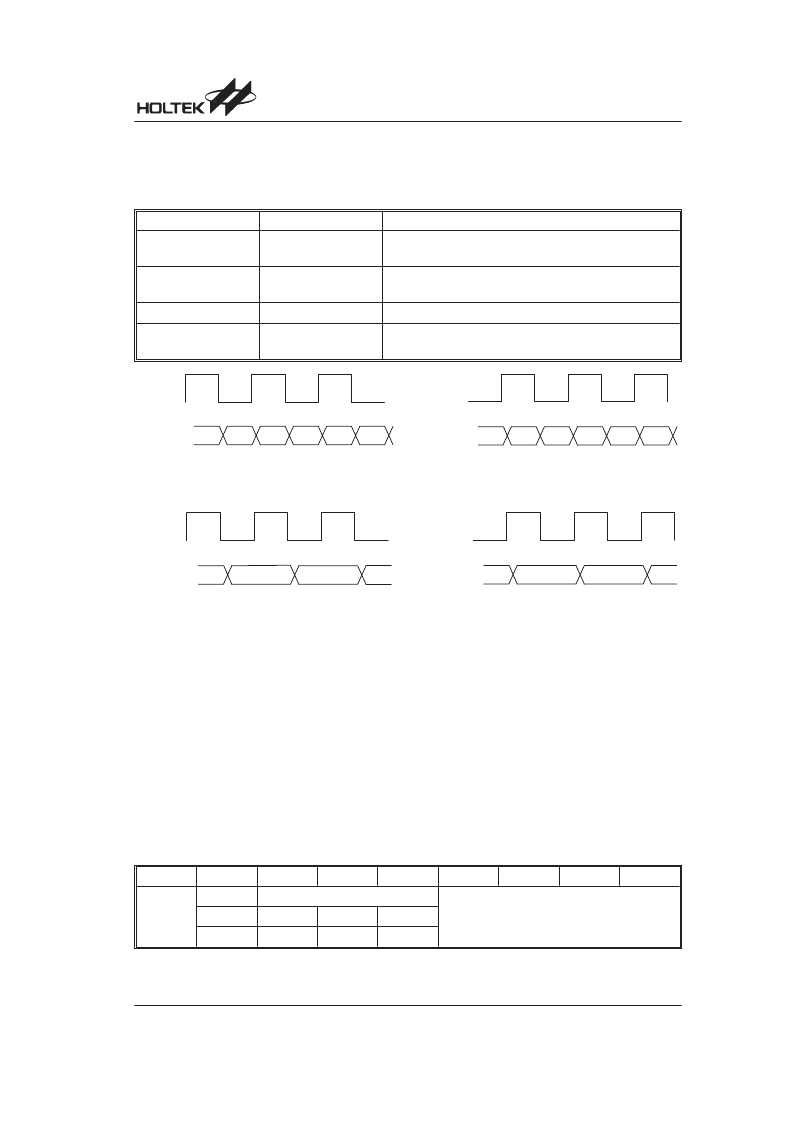

Bit D0 control the ADC output cycle of the HT82V24.

Bit D8 selects the ADC data output format selection. Setting D8 high enables the WM mode data output format while

settingbitD8lowenablestheADImodeoutputdataformat.TheonenibbledatawilloutputdatatopinsD7~D4and4 4

(WM) mode output the data format selected. The output format as the following table:

D8

D0

ADC Output Format

0

0

D5=1: 3-CH 8 2 (ADI)

D5=0: 1 or 2-CH 8 2 (ADI)

0

1

D5=1: 3-CH 8 1 (ADI)

D5=0: 1 or 2-CH 8 1 (ADI)

1

0

D5=0: 1-CH 4 4 (WM)

1

1

D5=1: 3-CH 8 2 (WM)

D5=0: 1-CH 8 2 (WM)

-

6

7 % ;

9 % ;

-

6

7 % ;

)

'

%

0 :

2

)

'

%

0 :

2

/

6

7 % ;

MUX Register

The MUX register controls the sampling channel order

and the 2-channel mode configuration in the HT82V24.

Bit D8 is used to set the output latency in ADC clock pe-

riod and is only valid when WM mode data output format

is selected. Bit D7 is used when operating in the

3-channel mode or the 2-channel mode. Setting bit D7

high will sequence the MUX to sample the red channel

first, then the green channel, and then the blue channel.

When in the 3-channel mode, the CDSCLK2 rising edge

always resets the MUX to sample the red channel first

(see timing diagrams). When bit D7 is set low, the chan-

nel order is reversed to blue first, green second, and red

third. The CDSCLK2 rising edge will always reset the

MUX to sample the blue channel first. Bits D6, D5 and

D4 are used when operating in 1 or 2-channel mode. Bit

D6 is set high to sample the red channel. Bit D5 is set

high to sample the green channel. Bit D4 is set high to

sample the blue channel. The MUX will remain station-

ary during 1-channel mode. The two channel mode is

selected by setting two of the channel select bits

(D4~D6) high. The MUX samples the channels in the or-

der selected by bit D7. In WM mode, Bits D0~D2 are

used to control the sampling point delay option. Bit D3 is

used to select the rising or falling edge on the CDSCLK1

input pin and generates an internal VSMP pulse. Bits

D0~D3 set to 0 in ADI Mode.

D8

D7

D6

D5

D4

D3

D2

D1

D0

Set to 0

MUX Order

Channel Select

Set to 0

1=R-G-B*

1=RED*

1=GREEN

1=BLUE

0=B-G-R

0=Off

0=Off*

0=Off*

MUX Register Settings (ADI Mode)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HT82V26A | 16-Bit CCD/CIS Analog Signal Processor |

| HT82V26 | 16-Bit CCD/CIS Analog Signal Processor |

| HT82V36 | 16-Bit CCD/CIS Analog Signal Processor |

| HT82V731 | Audio D/A Converter |

| HT82V732 | Protective Eyeglasses |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HT82V26 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:16-Bit CCD/CIS Analog Signal Processor |

| HT82V26A | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:16-Bit CCD/CIS Analog Signal Processor |

| HT82V36 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:16-Bit CCD/CIS Analog Signal Processor |

| HT82V38 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:16-Bit CCD/CIS Analog Signal Processor |

| HT82V42 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:Single-channel 16-Bit CCD/CIS Analog Signal Processor |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。