- 您現在的位置:買賣IC網 > PDF目錄9026 > IDTCSP2510DPGI8 (IDT, Integrated Device Technology Inc)IC CLK DVR PLL ZDB 1:10 24TSSOP PDF資料下載

參數資料

| 型號: | IDTCSP2510DPGI8 |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁數: | 1/9頁 |

| 文件大小: | 0K |

| 描述: | IC CLK DVR PLL ZDB 1:10 24TSSOP |

| 標準包裝: | 3,000 |

| 類型: | 驅動器,PLL,零延遲緩沖器 |

| PLL: | 帶旁路 |

| 輸入: | 時鐘 |

| 輸出: | 時鐘 |

| 電路數: | 1 |

| 比率 - 輸入:輸出: | 1:10 |

| 差分 - 輸入:輸出: | 無/無 |

| 頻率 - 最大: | 175MHz |

| 除法器/乘法器: | 無/無 |

| 電源電壓: | 3 V ~ 3.6 V |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 24-TSSOP(0.173",4.40mm 寬) |

| 供應商設備封裝: | 24-TSSOP |

| 包裝: | 帶卷 (TR) |

| 其它名稱: | CSP2510DPGI8 |

1

0

°CTO85°CTEMPERATURERANGE

IDTCSP2510D

3.3V PHASE-LOCK LOOP CLOCK DRIVER

OCTOBER 2001

2001 Integrated Device Technology, Inc.

DSC-5874/3

c

IDTCSP2510D

0C TO 85C TEMPERATURE RANGE

3.3V PHASE-LOCK LOOP

CLOCK DRIVER

ZERO DELAY BUFFER

DESCRIPTION:

The CSP2510D is a high performance, low-skew, low-jitter, phase-lock

loop (PLL) clock driver. It uses a PLL to precisely align, in both frequency

and phase, the feedback (FBOUT) output to the clock (CLK) input signal.

It is specifically designed for use with synchronous DRAMs. The CSP2510D

operates at 3.3V.

One bank of ten outputs provide low-skew, low-jitter copies of CLK.

Output signal duty cycles are adjusted to 50 percent, independent of the duty

cycle at CLK. The outputs can be enabled or disabled via the control G input.

When the G input is high, the outputs switch in phase and frequency with

CLK; when the G input is low, the outputs are disabled to the logic-low state.

Unlike many products containing PLLs, the CSP2510D does not require

external RC networks. The loop filter for the PLL is included on-chip,

minimizing component count, board space, and cost.

Because it is based on PLL circuitry, the CSP2510D requires a

stabilization time to achieve phase lock of the feedback signal to the

reference signal. This stabilization time is required, following power up and

application of a fixed-frequency, fixed-phase signal at CLK, as well as

following any changes to the PLL reference or feedback signals. The PLL

can be bypassed for the test purposes by strapping AVDD to ground.

The CSP2510D is specified for operation from 0°C to +85°C. This device

is also available (on special order) in Industrial temperature range (-40°C

to +85°C). See ordering information for details.

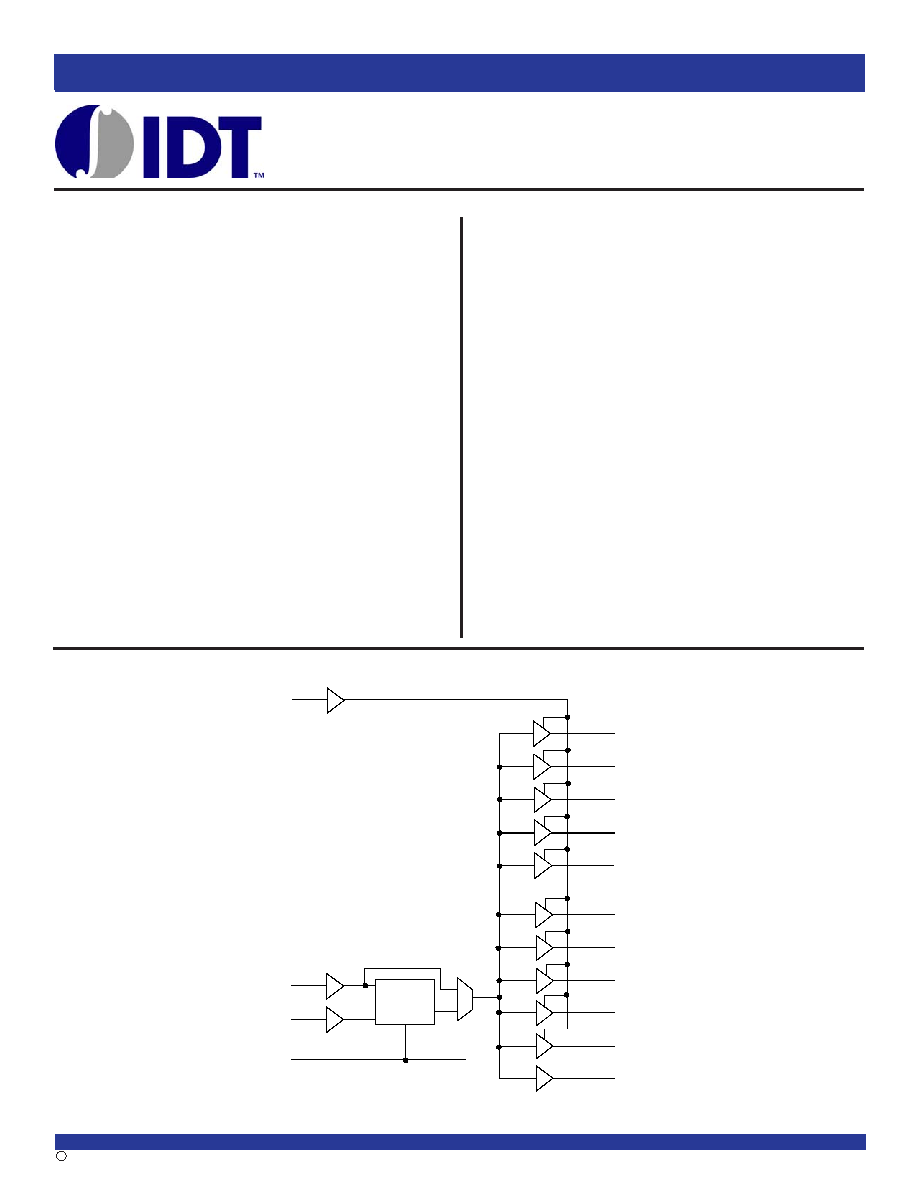

21

Y9

PLL

3

5

8

9

4

Y0

Y1

Y2

Y3

Y4

15

17

20

16

Y5

Y6

Y7

Y8

24

13

23

AVDD

FBIN

CLK

G

11

12

FBOUT

FUNCTIONAL BLOCK DIAGRAM

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

FEATURES:

Phase-Lock Loop Clock Distribution for Synchronous DRAM

Applications

Distributes one clock input to one bank of ten outputs

Output enable bank control

External feedback (FBIN) pin is used to synchronize the

outputs to the clock input signal

No external RC network required for PLL loop stability

Operates at 3.3V VDD

tpd Phase Error at 166MHz: < ±150ps

Jitter (peak-to-peak) at 166MHz: < ±75ps @ 166MHz

Spread Spectrum Compatible

Operating frequency 50MHz to 175MHz

Available in 24-Pin TSSOP package

APPLICATIONS:

SDRAM Modules

PC Motherboards

Workstations

相關PDF資料 |

PDF描述 |

|---|---|

| VE-B31-MV-F3 | CONVERTER MOD DC/DC 12V 150W |

| VE-B31-MV-F2 | CONVERTER MOD DC/DC 12V 150W |

| W134MHT | IC CLK DIFF DIRECT RAMBUS 24QSOP |

| VE-2NY-MU-F4 | CONVERTER MOD DC/DC 3.3V 132W |

| VE-23P-MW-F4 | CONVERTER MOD DC/DC 13.8V 100W |

相關代理商/技術參數 |

參數描述 |

|---|---|

| IDTCSP5940Q | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Ten Distributed-Output Clock Driver |

| IDTCSPF2510C | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:3.3V PHASE-LOCK LOOP CLOCK DRIVER |

| IDTCSPF2510CPG | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:3.3V PHASE-LOCK LOOP CLOCK DRIVER |

| IDTCSPF2510CPGG | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:3.3V PHASE-LOCK LOOP CLOCK DRIVER |

| IDTCSPF2510CPGGI | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:3.3V PHASE-LOCK LOOP CLOCK DRIVER |

發布緊急采購,3分鐘左右您將得到回復。