- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367533 > LC4512B-35F256C PDF資料下載

參數(shù)資料

| 型號(hào): | LC4512B-35F256C |

| 文件頁(yè)數(shù): | 19/57頁(yè) |

| 文件大小: | 1078K |

| 代理商: | LC4512B-35F256C |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)當(dāng)前第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)

Lattice Semiconductor

ispMACH 4000V/B/C Family Data Sheet

19

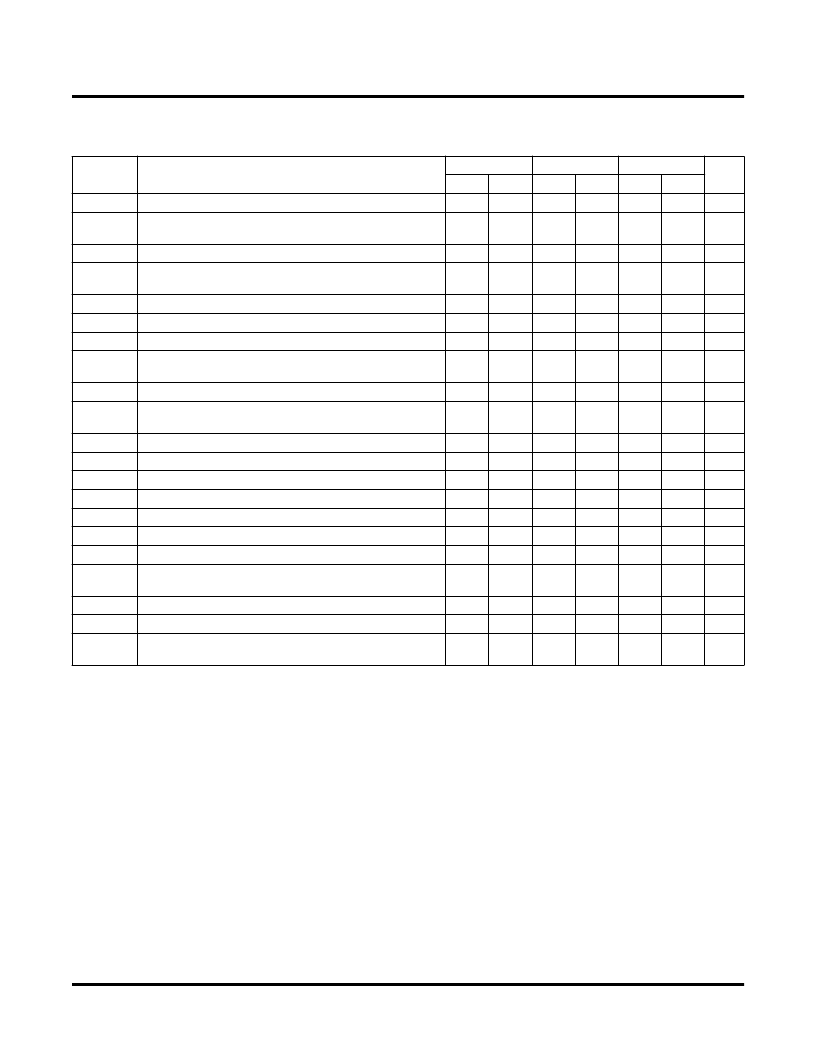

ispMACH 4000V/B/C External Switching Characteristics (Cont.)

Over Recommended Operating Conditions

Parameter

t

PD

Description

1, 2, 3

-5

-75

-10

5

Units

ns

ns

Min.

—

—

Max.

5.0

5.5

Min.

—

—

Max.

7.5

8.0

Min.

—

—

Max.

10.0

10.5

5-PT bypass combinatorial propagation delay

20-PT combinatorial propagation delay through macro-

cell

GLB register setup time before clock

GLB register setup time before clock with

T-type register

GLB register setup time before clock, input register path

GLB register setup time before clock with zero hold

GLB register hold time after clock

GLB register hold time after clock with

T-type register

GLB register hold time after clock, input register path

GLB register hold time after clock, input register path with

zero hold

GLB register clock-to-output delay

External reset pin to output delay

External reset pulse duration

Input to output local product term output enable/disable

Input to output global product term output enable/disable

Global OE input to output enable/disable

Global clock width, high or low

Global gate width low (for low transparent) or high (for

high transparent)

Input register clock width, high or low

Clock frequency with internal feedback

Clock frequency with external feedback,

[1/ (t

S

+ t

CO

)]

t

PD_MC

t

S

3.0

3.2

—

—

4.5

4.7

—

—

5.5

5.5

—

—

ns

ns

t

ST

t

SIR

t

SIRZ

t

H

1.2

2.2

0.0

0.0

—

—

—

—

1.7

2.7

0.0

0.0

—

—

—

—

1.7

2.7

0.0

0.0

—

—

—

—

ns

ns

ns

ns

t

HT

t

HIR

1.0

0.0

—

—

1.0

0.0

—

—

1.0

0.0

—

—

ns

t

HIRZ

ns

t

CO

t

R

t

RW

t

PTOE/DIS

t

GPTOE/DIS

t

GOE/DIS

t

CW

—

—

2.0

—

—

—

2.2

2.2

3.40

6.30

—

7.00

9.00

5.00

—

—

—

—

4.0

—

—

—

3.3

3.3

4.5

9.0

—

9.0

10.3

7.0

—

—

—

—

4.0

—

—

—

4.0

4.0

6.0

10.5

—

10.5

12.0

8.0

—

—

ns

ns

ns

ns

ns

ns

ns

t

GW

ns

t

WIR

f

MAX

2.2

227

156

—

—

—

3.3

168

111

—

—

—

4.0

125

86

—

—

—

ns

MHz

4

f

MAX

(Ext.)

MHz

Timing v.3.1

1. Timing numbers are based on default LVCMOS 1.8 I/O buffers. Use timing adjusters provided to calculate other standards.

2. Measured using standard switching circuit, assuming GRP loading of 1 and 1 output switching.

3. Pulse widths and clock widths less than minimum will cause unknown behavior.

4. Standard 16-bit counter using GRP feedback.

5. Only available in industrial grade.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LC4512B-35T176C | |

| LC4512B-5F256C | |

| LC4512B-5F256I | |

| LC4512B-5T176C | |

| LC4512B-5T176I | |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LC4512B-35F256C1 | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:3.3V/2.5V/1.8V In-System Programmable SuperFAST High Density PLDs |

| LC4512B-35FN256C | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 PROGRAMMABLE SUPER FAST HI DENSITY PLD RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| LC4512B-35FN256C1 | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:3.3V/2.5V/1.8V In-System Programmable SuperFAST High Density PLDs |

| LC4512B-35FT256C | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 ispJTAG 2.5V 3.5ns 512MC 208 I/O RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| LC4512B-35FTN256C | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 ispJTAG 2.5V 3.5ns 512MC 208 I/O RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。