- 您現在的位置:買賣IC網 > PDF目錄30744 > LM1882RE/883 (NATIONAL SEMICONDUCTOR CORP) SPECIALTY CONSUMER CIRCUIT, CQCC20 PDF資料下載

參數資料

| 型號: | LM1882RE/883 |

| 廠商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分類: | 消費家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, CQCC20 |

| 封裝: | CERAMIC, LCC-20 |

| 文件頁數: | 10/16頁 |

| 文件大小: | 236K |

| 代理商: | LM1882RE/883 |

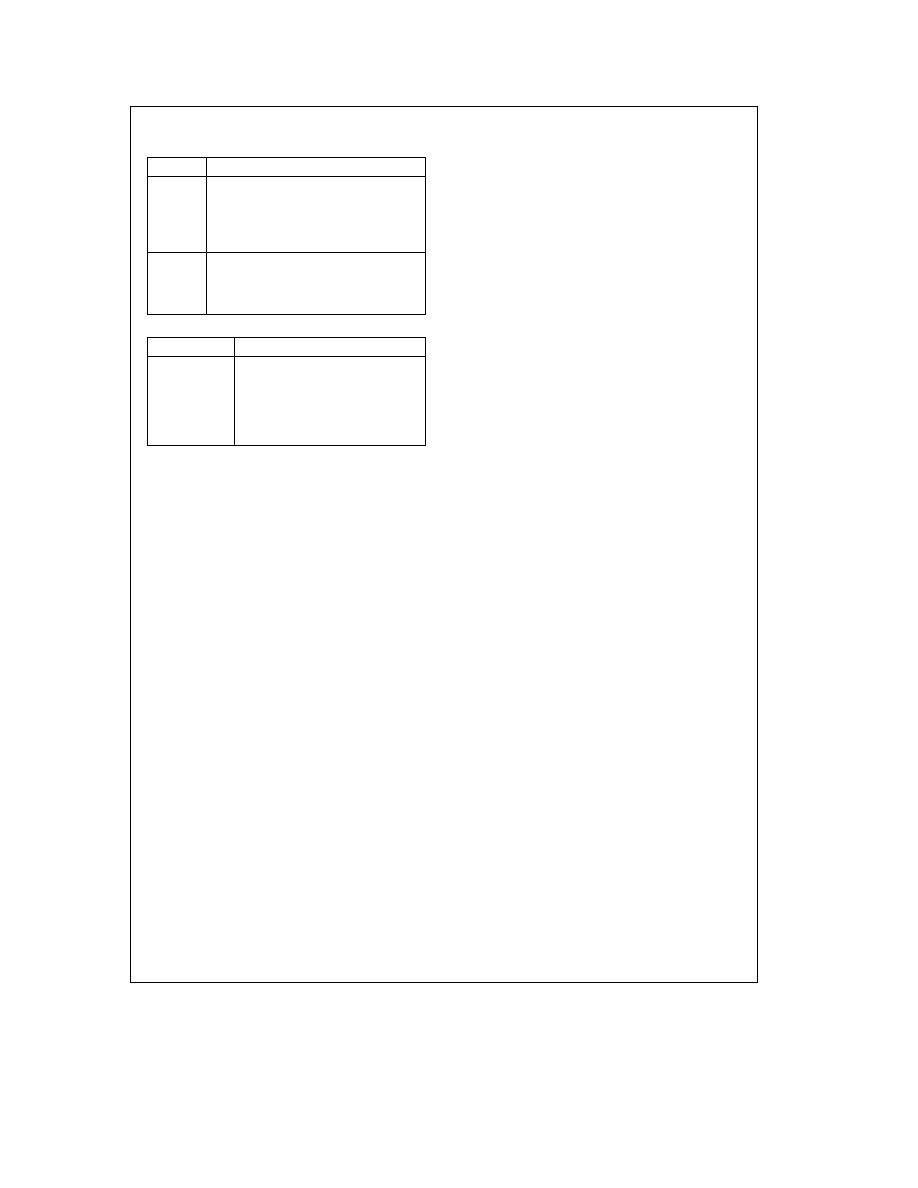

Register Description (Continued)

Bits 0 – 2

B2 B1 B0 VCBLANK VCSYNC HBLHDR HSYNVDR

0

CBLANK

CSYNC

HGATE

VGATE

(DEFAULT)

0

1

VBLANK

CSYNC

HBLANK

VGATE

0

1

0

CBLANK

VSYNC

HGATE

HSYNC

0

1

VBLANK

VSYNC

HBLANK

HSYNC

1

0

CBLANK

CSYNC

CURSOR

VINT

1

0

1

VBLANK

CSYNC

HBLANK

VINT

1

0

CBLANK

VSYNC

CURSOR

HSYNC

1

VBLANK

VSYNC

HBLANK

HSYNC

Bits 3 – 4

B4

B3

Mode of Operation

0

Interlaced Double Serration and

(DEFAULT)

Equalization

0

1

Non Interlaced Double Serration

1

0

Illegal State

1

Non Interlaced Single Serration

and Equalization

Double Equalization and Serration mode will output equali-

zation and serration pulses at twice the HSYNC frequency

(ie

2 equalization or serration pulses for every HSYNC

pulse) Single Equalization and Serration mode will output

an equalization or serration pulse for every HSYNC pulse In

Interlaced mode equalization and serration pulses will be

output during the VBLANK period of every odd and even

field Interlaced Single Equalization and Serration mode is

not possible with this part

Bits 5 – 8

Bits 5 through 8 control the polarity of the outputs A value

of zero in these bit locations indicates an output pulse active

LOW A value of 1 indicates an active HIGH pulse

B5

VCBLANK Polarity

B6

VCSYNC Polarity

B7

HBLHDR Polarity

B8

HSYNVDR Polarity

Bits 9 – 11

Bits 9 through 11 enable several different features of the

device

B9

Enable EqualizationSerration Pulses (0)

Disable EqualizationSerration Pulses (1)

B10

Disable System Clock (0)

Enable System Clock (1)

Default values for B10 are ‘‘0’’ in the ’ACT715

LM1882 and ‘‘1’’ in the ’ACT715-RLM1882-R

B11

Disable Counter Test Mode (0)

Enable Counter Test Mode (1)

This bit is not intended for the user but is for internal

testing only

HORIZONTAL INTERVAL REGISTERS

The Horizontal Interval Registers determine the number of

clock cycles per line and the characteristics of the Horizon-

tal Sync and Blank pulses

REG1

Horizontal Front Porch

REG2

Horizontal Sync Pulse End Time

REG3

Horizontal Blanking Width

REG4

Horizontal Interval Width

of Clocks per Line

VERTICAL INTERVAL REGISTERS

The Vertical Interval Registers determine the number of

lines per frame and the characteristics of the Vertical Blank

and Sync Pulses

REG5

Vertical Front Porch

REG6

Vertical Sync Pulse End Time

REG7

Vertical Blanking Width

REG8

Vertical Interval Width

of Lines per Frame

EQUALIZATION AND SERRATION PULSE

SPECIFICATION REGISTERS

These registers determine the width of equalization and ser-

ration pulses and the vertical interval over which they occur

REG 9

Equalization Pulse Width End Time

REG10

Serration Pulse Width End Time

REG11

EqualizationSerration Pulse Vertical

Interval Start Time

REG12

EqualizationSerration Pulse Vertical

Interval End Time

VERTICAL INTERRUPT SPECIFICATION REGISTERS

These Registers determine the width of the Vertical Inter-

rupt signal if used

REG13

Vertical Interrupt Activate Time

REG14

Vertical Interrupt Deactivate Time

CURSOR LOCATION REGISTERS

These 4 registers determine the cursor position location or

they generate separate Horizontal and Vertical Gating sig-

nals

REG15

Horizontal Cursor Position Start Time

REG16

Horizontal Cursor Position End Time

REG17

Vertical Cursor Position Start Time

REG18

Vertical Cursor Position End Time

Signal Specification

HORIZONTAL SYNC AND BLANK

SPECIFICATIONS

All horizontal signals are defined by a start and end time

The start and end times are specified in number of clock

cycles per line The start of the horizontal line is considered

pulse 1 not 0 All values of the horizontal timing registers are

referenced to the falling edge of the Horizontal Blank signal

(see

Figure 1 ) Since the first CLOCK edge CLOCK

1

causes the first falling edge of the Horizontal Blank refer-

ence pulse edges referenced to this first Horizontal edge

are n a 1 CLOCKs away where ‘‘n’’ is the width of the

timing in question Registers 1 2 and 3 are programmed in

this manner The horizontal counters start at 1 and count

until HMAX The value of HMAX must be divisible by 2 This

3

相關PDF資料 |

PDF描述 |

|---|---|

| LM1882RJ/883 | SPECIALTY CONSUMER CIRCUIT, CDIP20 |

| LM1882EV | SPECIALTY CONSUMER CIRCUIT, PQCC20 |

| LM1882-REV | SPECIALTY CONSUMER CIRCUIT, CQCC20 |

| LM1894M/NOPB | SPECIALTY CONSUMER CIRCUIT, PDSO14 |

| LM1894MDC | SPECIALTY CONSUMER CIRCUIT, UUC |

相關代理商/技術參數 |

參數描述 |

|---|---|

| LM1884 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:TV STEREO DECODER |

| LM1884N | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:TV STEREO DECODER |

| LM1886 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:TV Video Matrix D to A |

| LM1886N | 制造商:Texas Instruments 功能描述: |

| LM1886N/B+ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Color Encoder Circuit |

發布緊急采購,3分鐘左右您將得到回復。