- 您現在的位置:買賣IC網 > PDF目錄377652 > LMU112PC50 (LOGIC DEVICES INC) 12 x 12-bit Parallel Multiplier PDF資料下載

參數資料

| 型號: | LMU112PC50 |

| 廠商: | LOGIC DEVICES INC |

| 元件分類: | 數字信號處理外設 |

| 英文描述: | 12 x 12-bit Parallel Multiplier |

| 中文描述: | 12-BIT, DSP-MULTIPLIER, PDIP48 |

| 封裝: | PLASTIC, DIP-48 |

| 文件頁數: | 1/6頁 |

| 文件大小: | 46K |

| 代理商: | LMU112PC50 |

DEVICES INCORPORATED

LMU112

12 x 12-bit Parallel Multiplier

12 x 12-bit Parallel Multiplier

Multipliers

08/16/2000–LDS.112-K

1

K

25 ns Worst-Case Multiply Time

K

Low Power CMOS Technology

K

Replaces Fairchild MPY112K

K

Two’s Complement or Unsigned

Operands

K

Three-State Outputs

K

Package Styles Available:

48-pin PDIP

52-pin PLCC, J-Lead

FEATURES

DESCRIPTION

DEVICES INCORPORATED

The

LMU112

is a high-speed, low

power 12-bit parallel multiplier built

using advanced CMOS technology.

The LMU112 is pin and functionally

compatible with Fairchilds’s MPY112K.

The A and B input operands are

loaded into their respective registers

on the rising edge of the separate

clock inputs (CLK A and CLK B).

Two’s complement or unsigned

magnitude operands are accommo-

dated via the operand control bit (TC)

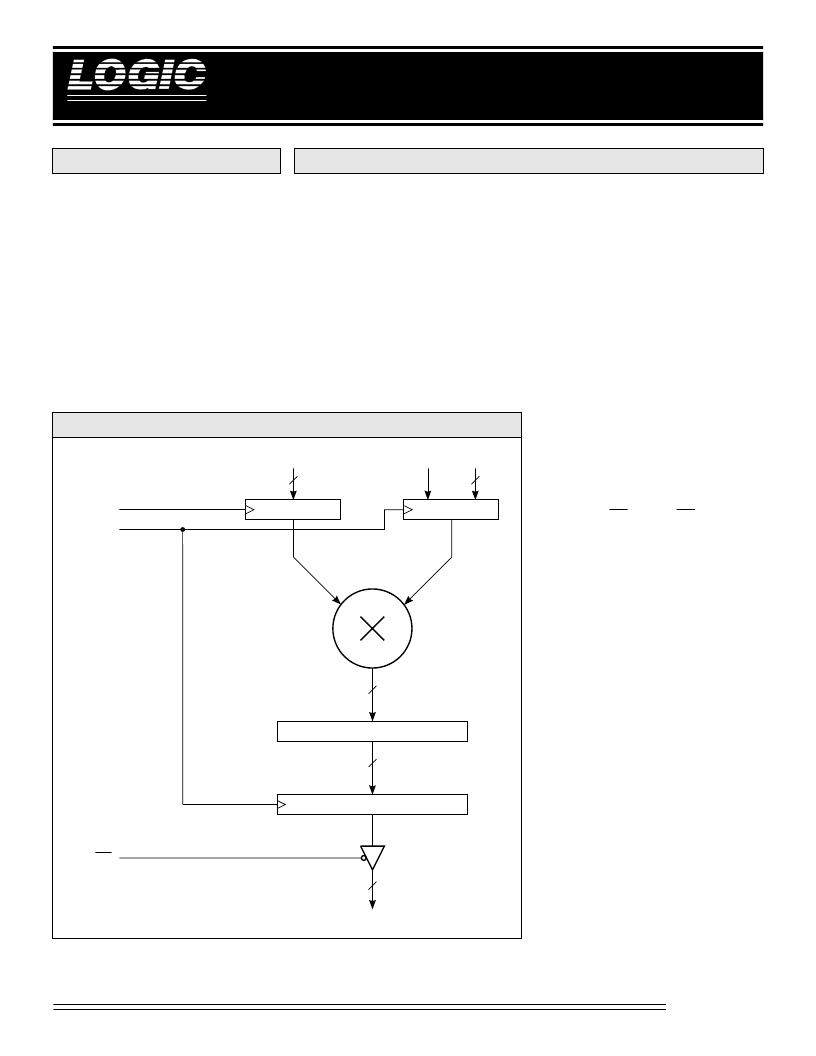

LMU112 B

LOCK

D

IAGRAM

A REGISTER

CLK A

CLK B

12

12

24

OE

B

11-0

A

11-0

R

23-8

TC

FORMAT ADJUST

16

B REGISTER

RESULT REGISTER

16

which is loaded along with the B

operands. The operands are specified

to be in two’s complement format

when TC is asserted and unsigned

magnitude when TC is deasserted.

Mixed mode operation is not allowed.

For two’s complement operands, the

17 most significant bits at the output

of the asynchronous multiplier array

are shifted one bit position to the left.

This is done to discard the redundant

copy of the sign-bit, which is in the

most significant bit position, and

extend the bit precision by one bit.

The result is then truncated to the 16

MSB’s and loaded into the output

register on the rising edge of CLK B.

The contents of the output register are

made available via three-state buffers

by asserting OE. When OE is de-

asserted, the outputs (R

23-8

) are in the

high impedance state.

相關PDF資料 |

PDF描述 |

|---|---|

| LMU216 | High-Speed, Low Power, 16-Bit Parallel Multiplier(高速,低功耗,16位并行乘法器) |

| LMU16 | 16 x 16-bit Parallel Multiplier |

| LMU216JC20 | 16 x 16-bit Parallel Multiplier |

| LMU216JC25 | 16 x 16-bit Parallel Multiplier |

| LMU217JC25 | GIGATRUE 550 CAT PATCH CBL NO BOOT 30FT YW 25 PK |

相關代理商/技術參數 |

參數描述 |

|---|---|

| LMU112PC60 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Multiplier |

| LMU112PCR | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Logic IC |

| LMU112PCR50 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Logic IC |

| LMU12DC35 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Multiplier |

| LMU12DC45 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Multiplier |

發布緊急采購,3分鐘左右您將得到回復。