- 您現在的位置:買賣IC網 > PDF目錄361044 > LMX2354TM (NATIONAL SEMICONDUCTOR CORP) PLLatinum Fractional N RF/ Integer N IF Dual Low Power Frequency Synthesizer PDF資料下載

參數資料

| 型號: | LMX2354TM |

| 廠商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分類: | XO, clock |

| 英文描述: | PLLatinum Fractional N RF/ Integer N IF Dual Low Power Frequency Synthesizer |

| 中文描述: | PLL FREQUENCY SYNTHESIZER, 2500 MHz, PDSO24 |

| 封裝: | PLASTIC, TSSOP-24 |

| 文件頁數: | 15/23頁 |

| 文件大小: | 403K |

| 代理商: | LMX2354TM |

Programming Description

(Continued)

4.2.1 (RF_R[22]–RF_R[23])

DLL_MODE

V2_EN

BIT

DLL_MODE

LOCATION

RF_R [23]

FUNCTION

Delay Line Loop

Calibration Mode

RF_Voltage Doubler

Enable

0

1

Slow

Fast

V2_EN

RF_R [22]

Disabled

Enabled

Note 1.

V2_EN bit when set high enables the voltage doubler for the RF Charge Pump supply.

Note 2.

DLL_MODE bit should be set to one for normal usage.

4.2.2 RF_CP_WORD

(RF_R[17]–RF_R[21])

CP_8X

CP_4X

CP_2X

CP_1X

RF_PD_POL

RF_PD_POL

( RF_R[17] ) should be set to one when RF VCO characteristics are positive. When RF VCO frequency decreases

with increasing control voltage RF_PD_POL should be set to zero.

CP_1X, CP_2X, CP_4X, and CP_8X

are used to step the RF Charge Pump output current magnitude from 100 μA to 1.6 mA in

100 μA steps as shown in the table below.

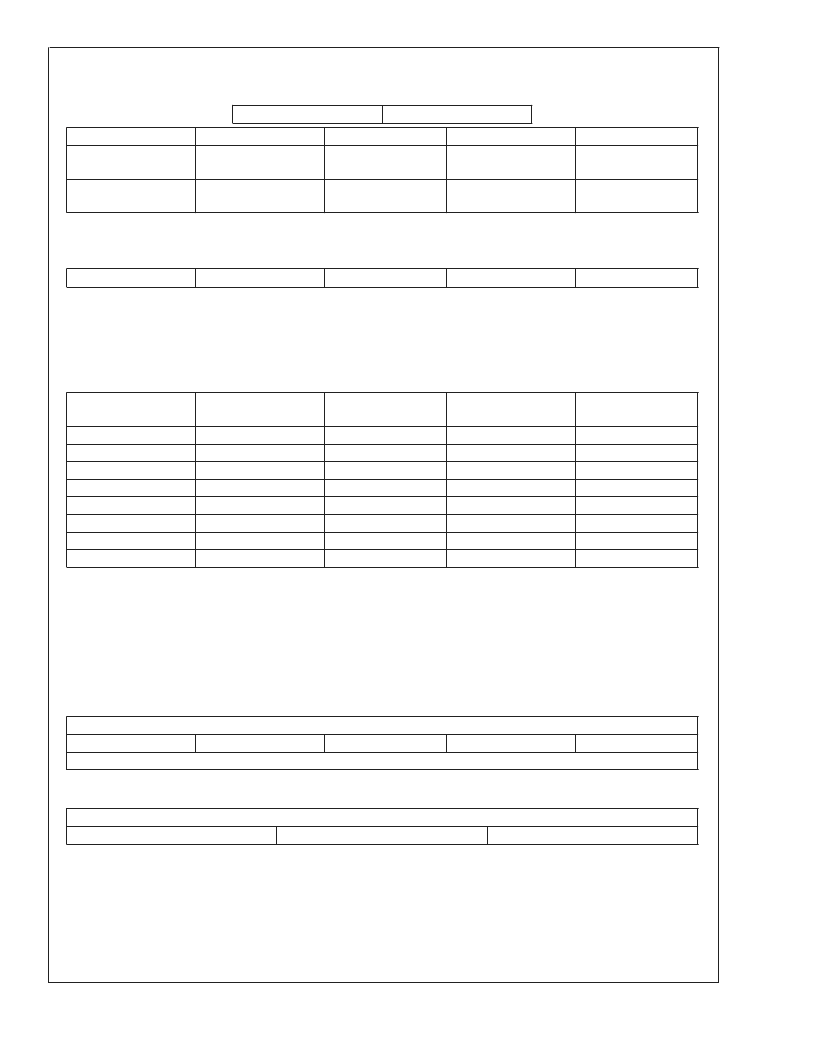

RF Charge Pump Output Truth Table

ICPo μA (typ)

CP8X

RF_R[21]

0

0

0

0

1

1

CP4X

RF_R[20]

0

0

0

0

0

1

CP2X

RF_R[19]

0

0

1

1

0

1

CP1X

RF_R[18]

0

1

0

1

0

1

100

200

300

400

900

1600

5.0 Programmable Dividers (N Counters)

5.1 IF_N REGISTER

If the Control Bits (CTL [1:0]) are 0 1, data is transferred from the 24-bit shift register into the IF_N register latch which sets the

PLL’s 15-bit programmable N counter value and various control functions. The IF_N counter consists of the 3-bit swallow counter

(A counter), and the 12-bit programmable counter (B counter). Serial data format is shown below in tables 5.1.3 and 5.1.4. The

divide ratio (IF_NB_CNTR) must be

≥

3. The divide ratio is programmed using the bits IF_N_CNTR as shown in tables 5.1.2 and

5.1.3. The minimum continuous divide ratio is 56. The CMOS [3:0] bits program the 2 CMOS outputs detailed in section 5.1.2, and

also contain the fractional test bit.

MSB

IF_CTL_WORD [2:0]

23

LSB

CMOS [3:0]

21 20

IF_NB_CNTR [11:0]

17 16

IF_NA_CNTR [2:0]

5 4

0

1

0

2 1

5.1.1 IF_CTL_WORD

(IF_N[21]–IF_N[23])

MSB

IF_CNT_RST

LSB

PWDN_IF

PWDN_MODE

Note:

See section 5.2.1.2 for IF control word truth table.

L

www.national.com

15

相關PDF資料 |

PDF描述 |

|---|---|

| LMX2354 | PLLatinum Fractional N RF/ Integer N IF Dual Low Power Frequency Synthesizer |

| LMX2355TM | PLLatinum Fractional N RF/ Integer N IF Dual Low Power Frequency Synthesizer |

| LMX2354SLB | PLLatinum Fractional N RF/ Integer N IF Dual Low Power Frequency Synthesizer |

| LMX2355SLB | PLLatinum Fractional N RF/ Integer N IF Dual Low Power Frequency Synthesizer |

| LMX2430 | PLLatinum Dual High Frequency Synthesizer for RF Personal Communications |

相關代理商/技術參數 |

參數描述 |

|---|---|

| LMX2354TM | 制造商:Texas Instruments 功能描述:2.5GHZ/550MHZ PLL 2354 TSSOP24 |

| LMX2354TM/NOPB | 功能描述:IC PLATINUM SYNTHESIZER 24TSSOP RoHS:是 類別:集成電路 (IC) >> 時鐘/計時 - 時鐘發生器,PLL,頻率合成器 系列:PLLatinum™ 標準包裝:39 系列:- 類型:* PLL:帶旁路 輸入:時鐘 輸出:時鐘 電路數:1 比率 - 輸入:輸出:1:10 差分 - 輸入:輸出:是/是 頻率 - 最大:170MHz 除法器/乘法器:無/無 電源電壓:2.375 V ~ 3.465 V 工作溫度:0°C ~ 70°C 安裝類型:* 封裝/外殼:* 供應商設備封裝:* 包裝:* |

| LMX2354TMX/NOPB | 功能描述:IC FREQ SYNTH 2.5GHZ 24-TSSOP RoHS:是 類別:集成電路 (IC) >> 時鐘/計時 - 時鐘發生器,PLL,頻率合成器 系列:PLLatinum™ 標準包裝:39 系列:- 類型:* PLL:帶旁路 輸入:時鐘 輸出:時鐘 電路數:1 比率 - 輸入:輸出:1:10 差分 - 輸入:輸出:是/是 頻率 - 最大:170MHz 除法器/乘法器:無/無 電源電壓:2.375 V ~ 3.465 V 工作溫度:0°C ~ 70°C 安裝類型:* 封裝/外殼:* 供應商設備封裝:* 包裝:* |

| LMX2355SLB | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:PLLatinum Fractional N RF/ Integer N IF Dual Low Power Frequency Synthesizer |

| LMX2355TM | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:PLLatinum Fractional N RF/ Integer N IF Dual Low Power Frequency Synthesizer |

發布緊急采購,3分鐘左右您將得到回復。