- 您現在的位置:買賣IC網 > PDF目錄361044 > LMX2354TM (NATIONAL SEMICONDUCTOR CORP) PLLatinum Fractional N RF/ Integer N IF Dual Low Power Frequency Synthesizer PDF資料下載

參數資料

| 型號: | LMX2354TM |

| 廠商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分類: | XO, clock |

| 英文描述: | PLLatinum Fractional N RF/ Integer N IF Dual Low Power Frequency Synthesizer |

| 中文描述: | PLL FREQUENCY SYNTHESIZER, 2500 MHz, PDSO24 |

| 封裝: | PLASTIC, TSSOP-24 |

| 文件頁數: | 16/23頁 |

| 文件大小: | 403K |

| 代理商: | LMX2354TM |

Programming Description

(Continued)

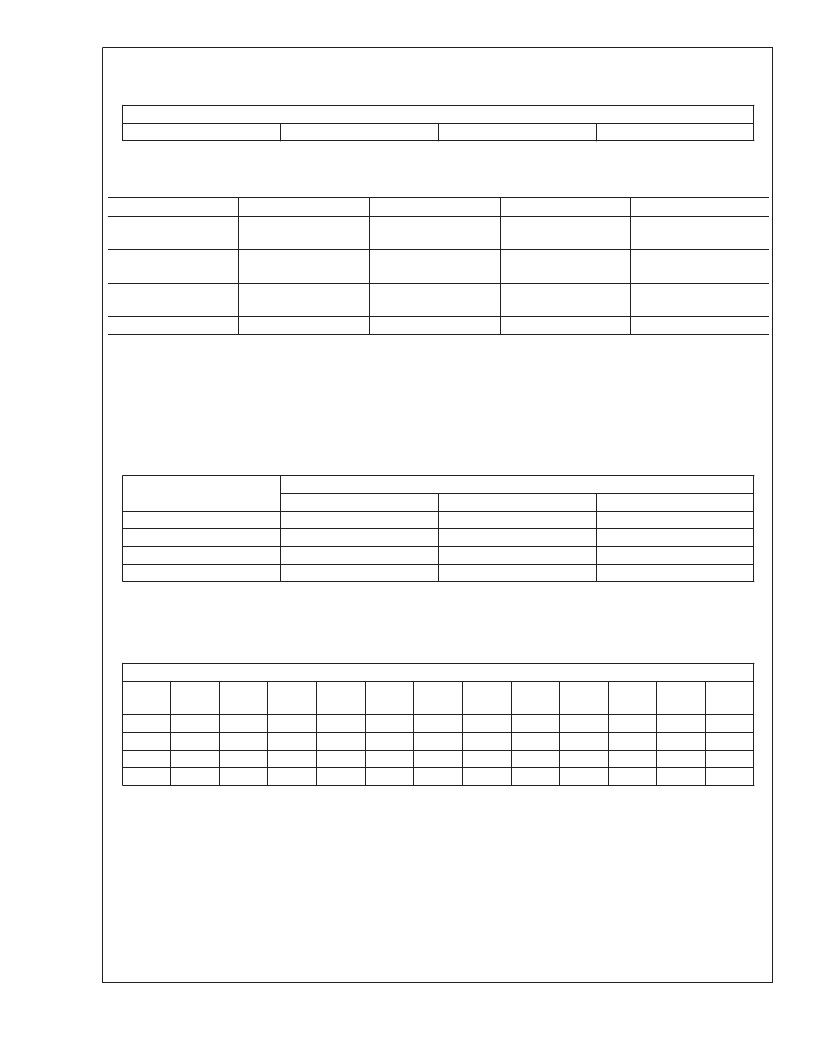

5.1.2 CMOS (Programmable CMOS outputs)

(IF_N[17]–IF_N[20])

MSB

LSB

FastLock

TEST

OUT_1

OUT_0

Note:

Test bit is reserved and should be set to zero for normal usage.

5.1.3 Programmable CMOS Output Truth Table

Bit

Location

IF_N[17]

Function

0

1

OUT_0

OUT0 CMOS Output Pin

Level Set

OUT1 CMOS Output Pin

Level Set

Fractional Test Bit

LOW

HIGH

OUT_1

IF_N[18]

LOW

HIGH

Test

IF_N[19]

Normal Operation

No Fractional

Compensation

Fastlock Mode

Fastlock

IF_N[20]

Fastlock Mode Select

CMOS Output

Test

Bit IF_N[19] controls the fractional spur compensation and should be set to 0 for normal operation. If the test bit is set to 1,

then the fractional spurs become much worse, but the phase noise improves about 5 dB.

When the

Fastlock

bit is set to 1,

OUT_0

and

OUT_1

are don’t care bits. Fastlock mode utilizes the OUT0 and OUT1 output pins

to synchronously switch between active low and TRI-STATE. The OUT0 = LOW state occurs whenever the RF loop’s CP_8X is

selected HIGH while the Fastlock bit is set HIGH (see programming description 4.2.2). The OUT0 pin reverts to TRI-STATE when

the CP_8X bit is LOW. Similarly for the IF loop, the synchronous activation of OUT1 = LOW or TRI-STATE, is dependent on

whether the CP_GAIN_8 is high or low respectively (see programming description 4.1.4).

5.1.4 3-BIT IF SWALLOW COUNTER DIVIDE RATIO (IF A COUNTER)

(IF_N[2]IF_N[4])

Swallow Count

(A)

0

1

7

IF_NA_CNTR

1

0

0

1

2

0

0

1

0

0

1

1

Note:

Swallow Counter Value: 0 to 7

IF_NB_CNTR

≥

IF_NA_CNTR

Minimum continuous count = 56 ( A=0, B=7)

5.1.5 12-BIT IF PROGRAMMABLE COUNTER DIVIDE RATIO (IF B COUNTER)

(IF_N[5]–IF_N[16])

IF_NB_CNTR

6

Divide

Ratio

3

4

4095

11

10

9

8

7

5

4

3

2

1

0

0

0

1

0

0

1

0

0

1

0

0

1

0

0

1

0

0

1

0

0

1

0

0

1

0

0

1

0

1

1

1

0

1

1

0

1

Note:

Divide ratio: 3 to 4095 (Divide ratios less than 3 are prohibited)

IF_NB_CNTR

≥

IF_NA_CNTR

N divider continuous integer divide ratio 56 to 32,767.

L

www.national.com

16

相關PDF資料 |

PDF描述 |

|---|---|

| LMX2354 | PLLatinum Fractional N RF/ Integer N IF Dual Low Power Frequency Synthesizer |

| LMX2355TM | PLLatinum Fractional N RF/ Integer N IF Dual Low Power Frequency Synthesizer |

| LMX2354SLB | PLLatinum Fractional N RF/ Integer N IF Dual Low Power Frequency Synthesizer |

| LMX2355SLB | PLLatinum Fractional N RF/ Integer N IF Dual Low Power Frequency Synthesizer |

| LMX2430 | PLLatinum Dual High Frequency Synthesizer for RF Personal Communications |

相關代理商/技術參數 |

參數描述 |

|---|---|

| LMX2354TM | 制造商:Texas Instruments 功能描述:2.5GHZ/550MHZ PLL 2354 TSSOP24 |

| LMX2354TM/NOPB | 功能描述:IC PLATINUM SYNTHESIZER 24TSSOP RoHS:是 類別:集成電路 (IC) >> 時鐘/計時 - 時鐘發生器,PLL,頻率合成器 系列:PLLatinum™ 標準包裝:39 系列:- 類型:* PLL:帶旁路 輸入:時鐘 輸出:時鐘 電路數:1 比率 - 輸入:輸出:1:10 差分 - 輸入:輸出:是/是 頻率 - 最大:170MHz 除法器/乘法器:無/無 電源電壓:2.375 V ~ 3.465 V 工作溫度:0°C ~ 70°C 安裝類型:* 封裝/外殼:* 供應商設備封裝:* 包裝:* |

| LMX2354TMX/NOPB | 功能描述:IC FREQ SYNTH 2.5GHZ 24-TSSOP RoHS:是 類別:集成電路 (IC) >> 時鐘/計時 - 時鐘發生器,PLL,頻率合成器 系列:PLLatinum™ 標準包裝:39 系列:- 類型:* PLL:帶旁路 輸入:時鐘 輸出:時鐘 電路數:1 比率 - 輸入:輸出:1:10 差分 - 輸入:輸出:是/是 頻率 - 最大:170MHz 除法器/乘法器:無/無 電源電壓:2.375 V ~ 3.465 V 工作溫度:0°C ~ 70°C 安裝類型:* 封裝/外殼:* 供應商設備封裝:* 包裝:* |

| LMX2355SLB | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:PLLatinum Fractional N RF/ Integer N IF Dual Low Power Frequency Synthesizer |

| LMX2355TM | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:PLLatinum Fractional N RF/ Integer N IF Dual Low Power Frequency Synthesizer |

發布緊急采購,3分鐘左右您將得到回復。