- 您現在的位置:買賣IC網 > PDF目錄361044 > LMX2433SLEX (NATIONAL SEMICONDUCTOR CORP) PLLatinum Dual High Frequency Synthesizer for RF Personal Communications PDF資料下載

參數資料

| 型號: | LMX2433SLEX |

| 廠商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分類: | XO, clock |

| 英文描述: | PLLatinum Dual High Frequency Synthesizer for RF Personal Communications |

| 中文描述: | PLL FREQUENCY SYNTHESIZER, 3600 MHz, PQCC20 |

| 封裝: | PLASTIC, UTCSP-20 |

| 文件頁數: | 37/49頁 |

| 文件大小: | 943K |

| 代理商: | LMX2433SLEX |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁當前第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁

1.0 Functional Description

(Continued)

1.8.4 Reference Divider and Feedback Divider Output

The outputs of the various N and R dividers can be moni-

tored by selecting the appropriate Ftest/LD word. This is

essential when performing OSCin or Fin sensitivity measure-

ments. Refer to the

LMX243x FinRF Sensitivity Test Setup

or

LMX243x OSCin Sensitivity Test Setup

sections for

more details. Note, the R and N outputs that are routed to

the Ftest/LD are R/2 and N/2 respectively. The internal /2

circuit is used to provide a 50% duty cycle. Refer to

Section

2.10

for more details on how to route the appropriate divider

output to the Ftest/LD pin.

1.9 FASTLOCK OUTPUT

The LMX243x Fastlock feature allows a faster loop response

time during lock aquisition. The loop response time (lock

time) can be approximately halved if the loop bandwidth is

doubled. In order to achieve this, the same gain/ phase

relationship should be maintained when the loop bandwidth

is doubled. When the FLoutRF or OSCout/ FLoutIF pins are

configured as FastLock outputs, an open drain device is

enabled. The open drain device switches in a resistor paral-

lel, and of equal value, to R2 of the external loop filter. The

loop bandwidth is effectively doubled and stability is main-

tained. Once locked to the correct frequency, the PLL will

return to a steady state condition.The LMX243x offers two

methods to achieve Fastlock: manual and automatic.

Manual Fastlock is achieved by increasing the charge pump

current from 1 mA (RF_CPG/ IF_CPG Bit = 0) in the steady

state mode, to 4 mA (RF_CPG/ IF_CPG Bit = 1) in Fastlock

mode. Automatic Fastlock is achieved by programming the

timeout counter register (RF_TOC/ IF_TOC) with the appro-

priate number of phase comparison cycles that the RF/ IF

synthesizer will spend in the Fastlock state. Refer to

Sec-

tions 2.6 and 2.9

for details on how to configure the

FLoutRF or OSCout/ FLoutIF output to an open drain Fast-

lock output.

1.10 COUNTER RESET

When the RF_RST/ IF_RST bit is enabled, both the feed-

back divider (RF_N/ IF_N) and reference divider (RF_R/

IF_R) are held at their load point. When the device is pro-

grammed to normal operation, both the feedback divider and

reference divder are enabled and resume counting in close

alignment to each other. Refer to

Sections 2.4.5 and 2.7.5

for more details.

1.11 POWER CONTROL

The LMX243x device can be asynchronously powered down

when the EN pin is set LOW, independent of the state of the

powerdown bits. Note that the OSCout/ FLoutIF pin can still

be enabled if the ENosc pin is set HIGH, independent of the

state of the EN pin. This capability allows the oscillator buffer

to be used as a crystal oscillator. When EN is set HIGH,

powerdown is controlled through the MICROWIRE. The

powerdown word is comprised of the

RF_PD

/

IF_PD

bit, in

conjuction with the

RF_CPT

/

IF_CPT

bit. The powerdown

control word is used to set the operating mode of the device.

Refer to

Sections 2.4.4, 2.5.4, 2.7.4

, and

2.8.4

for details on

how to program the RF or IF powerdown bits.

When either synthesizer is powered down, the respective

prescaler, phase detector, and charge pump circuit is dis-

abled. The CPoutRF/ CPoutIF, FinRF/ FinIF, and FinRF

*

pins are all forced to a high impedance state. The reference

divider and feedback divider circuits are held at the load

point during powerdown. The oscillator buffer is disabled

when the ENosc pin is set LOW. The OSCin pin is forced to

a HIGH state through an approximate 100 k

resistance

when this condition exists. When either synthesizer is acti-

vated, the respective prescaler, phase detector, charge

pump circuit, and the oscillator buffer are all powered up.

The feedback divider and reference divider are held at their

load point. This allows the reference oscillator, feedback

divider, reference divider and prescaler circuitry to reach

proper bias levels. After a finite delay, the feedback and

reference dividers are enabled and they resume counting in

close alignment (the maximum error is one prescaler cycle).

The MICROWIRE control register remains active and ca-

pable of loading and latching data while in powerdown

mode.

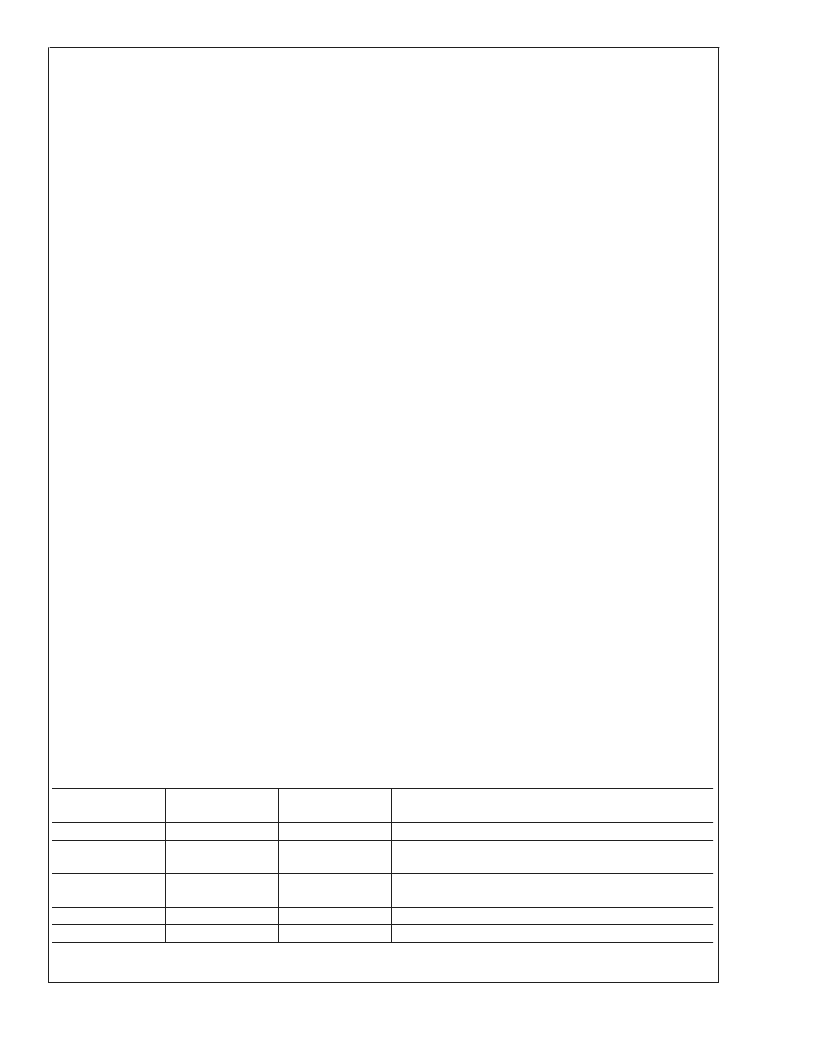

1.11.1 Synchronous Powerdown Mode

In this mode, the powerdown function is gated by the charge

pump. When the device is configured for synchronous pow-

erdown, the device will enter the powerdown mode upon

completion of the next charge pump pulse event.

1.11.2 Asynchronous Powerdown Mode

In this mode, the powerdown function is NOT gated by the

completion of a charge pump pulse event. When the device

is configured for asynchronous powerdown, the part will go

into powerdown mode immediately.

EN Pin

RF_CPT/

IF_CPT Bit

X

0

RF_PD/

IF_PD Bit

X

0

Operating Mode

0

1

Asynchronous Powerdown

PLL Active.

Normal Operation

PLL Active.

Charge Pump Output in High Impedance State

Synchronous Powerdown

Asynchronous Powerdown

1

1

0

1

1

0

1

1

1

Note:

X refers to a don’t care condition.

L

www.national.com

37

相關PDF資料 |

PDF描述 |

|---|---|

| LMX2434SLEX | PLLatinum Dual High Frequency Synthesizer for RF Personal Communications |

| LMX2531LQ1570E | PLLatinum High Performance Frequency Synthesizer System with Integrated VCO |

| LMX2531 | PLLatinum High Performance Frequency Synthesizer System with Integrated VCO |

| LMX2531LQ1650E | PLLatinum High Performance Frequency Synthesizer System with Integrated VCO |

| LMX2531LQ1778E | PLLatinum High Performance Frequency Synthesizer System with Integrated VCO |

相關代理商/技術參數 |

參數描述 |

|---|---|

| LMX2433SLEX/NOPB | 功能描述:鎖相環 - PLL RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| LMX2433TM | 制造商:Texas Instruments 功能描述:PLL Frequency Synthesizer Dual 250MHz to 3600MHz 20-Pin TSSOP Rail |

| LMX2433TM/NOPB | 功能描述:鎖相環 - PLL 3.6Ghz High Freq Dual Pll RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| LMX2433TMX | 功能描述:鎖相環 - PLL RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| LMX2433TMX/NOPB | 功能描述:鎖相環 - PLL RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

發布緊急采購,3分鐘左右您將得到回復。