- 您現在的位置:買賣IC網 > PDF目錄361044 > LMX2531LQ1700E (NATIONAL SEMICONDUCTOR CORP) PLLatinum High Performance Frequency Synthesizer System with Integrated VCO PDF資料下載

參數資料

| 型號: | LMX2531LQ1700E |

| 廠商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分類: | XO, clock |

| 英文描述: | PLLatinum High Performance Frequency Synthesizer System with Integrated VCO |

| 中文描述: | PLL FREQUENCY SYNTHESIZER, 80 MHz, QCC36 |

| 封裝: | 6 X 6 MM, 0.80 MM HEIGHT, LEAD FREE, LLP-36 |

| 文件頁數: | 3/25頁 |

| 文件大小: | 589K |

| 代理商: | LMX2531LQ1700E |

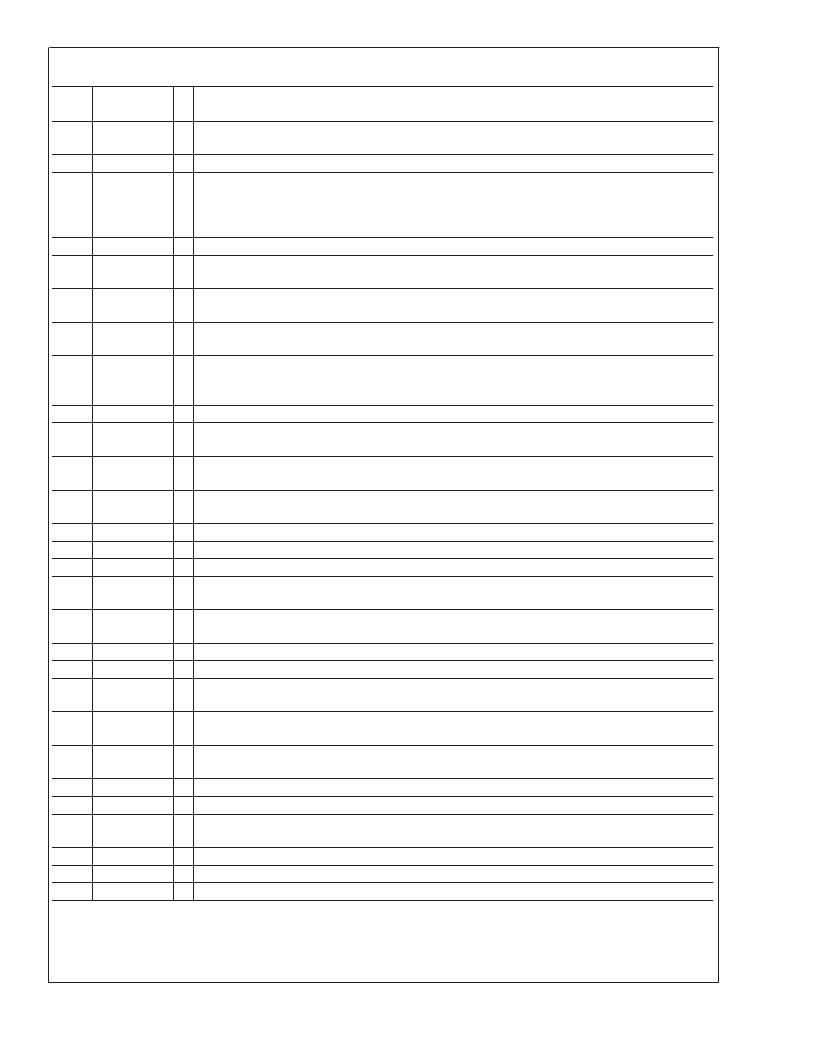

Pin Descriptions

Pin

Number

Pin Name

I/O Description

1

VccDIG

-

Power Supply for digital LDO circuitry. Input may range from 2.8 - 3.2 V. Bypass capacitors should be

placed as close as possible to this pin and ground.

Ground

3

GND

-

2,4,5,7,

12,

13,

29, 35

6

NC

-

No Connect.

VregBUF

-

Internally regulated voltage for the VCO buffer circuitry. Connect to ground with a capacitor.

MICROWIRE serial data input. High impedance CMOS input. This pin must not exceed 2.75V. Data is

clocked in MSB first. The last bits clocked in form the control or register select bits.

MICROWIRE clock input. High impedance CMOS input. This pin must not exceed 2.75V. Data is

clocked into the shift register on the rising edge.

MICROWIRE Latch Enable input. High impedance CMOS input. This pin must not exceed 2.75V.

Data stored in the shift register is loaded into the selected latch register when LE goes HIGH.

Chip Enable Input. High impedance CMOS input. This pin must not exceed 2.75V. When CE is

brought high the LMX2531 is powered up corresponding to the internal power control bits. It is

necessary to reprogram the R0 register to get the part to re-lock.

No Connect. Do NOT ground.

Power Supply for VCO regulator circuitry. Input may range from 2.8 - 3.2 V. Bypass capacitors should

be placed as close as possible to this pin and ground.

Internally regulated voltage for VCO circuitry. Not intended to drive an external load. Connect to

ground with a capacitor and some series resistance.

Internal reference voltage for VCO LDO. Not intended to drive an external load. Connect to ground

with a capacitor.

Ground for the VCO circuitry.

Ground for the RF Output Buffer circuitry.

O Buffered RF Output for the VCO.

Power Supply for the VCO Buffer circuitry. Input may range from 2.8 - 3.2 V. Bypass capacitors

should be placed as close as possible to this pin and ground.

Tuning voltage input for the VCO. For connection to the CPout Pin through an external passive loop

filter.

O Charge pump output for PLL. For connection to Vtune through an external passive loop filter.

O An open drain NMOS output which is used for FastLock or a general purpose output.

Internally regulated voltage for PLL charge pump. Not intended to drive an external load. Connect to

ground with a capacitor.

Power Supply for the PLL. Input may range from 2.8 - 3.2 V. Bypass capacitors should be placed as

close as possible to this pin and ground.

Internally regulated voltage for RF digital circuitry. Not intended to drive an external load. Connect to

ground with a capacitor.

O Multiplexed CMOS output. Typically used to monitor PLL lock condition.

I

Oscillator input. The oscillator can be placed in either single-ended or differential mode of operation.

Oscillator complimentary input. When a single ended source is used, then a bypass capacitor should

be placed as close as possible to this pin and be connected to ground.

O This pin if for test purposes and should be grounded for normal operation.

-

Ground

-

Internally regulated voltage for LDO digital circuitry.

8

DATA

I

9

CLK

I

10

LE

I

11

CE

I

14, 15

NC

-

16

VccVCO

-

17

VregVCO

-

18

VrefVCO

-

19

20

21

GND

GND

Fout

-

-

22

VccBUF

-

23

Vtune

I

24

25

CPout

FLout

26

VregPLL1

-

27

VccPLL

-

28

VregPLL2

-

30

31

Ftest/LD

OSCin

32

OSCin*

I

33

34

36

Test

GND

VregDIG

L

www.national.com

3

相關PDF資料 |

PDF描述 |

|---|---|

| LMX4268 | Radio Transceiver for DECT |

| LMX5080MX | PLLatinum⑩ 2.7 GHz Low Power Dual Modulus Prescaler for RF Personal Communications |

| LMX5080M | PLLatinum⑩ 2.7 GHz Low Power Dual Modulus Prescaler for RF Personal Communications |

| LMX5080 | PLLatinum⑩ 2.7 GHz Low Power Dual Modulus Prescaler for RF Personal Communications |

| LMX9820ASMX | Bluetooth Serial Port Module |

相關代理商/技術參數 |

參數描述 |

|---|---|

| LMX2531LQ1700E/NOPB | 功能描述:鎖相環 - PLL RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| LMX2531LQ1742 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Texas Instruments 功能描述:SYNTHESIZER SYSTEM POWERWISE SMD |

| LMX2531LQ1742/NOPB | 功能描述:鎖相環 - PLL RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| LMX2531LQ1742FPEB | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:Evaluation Board Operating Instructions |

| LMX2531LQ1778E | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:PLLatinum High Performance Frequency Synthesizer System with Integrated VCO |

發布緊急采購,3分鐘左右您將得到回復。