- 您現在的位置:買賣IC網 > PDF目錄361045 > LPC662 (National Semiconductor Corporation) Low Power CMOS Dual Operational Amplifier PDF資料下載

參數資料

| 型號: | LPC662 |

| 廠商: | National Semiconductor Corporation |

| 英文描述: | Low Power CMOS Dual Operational Amplifier |

| 中文描述: | 低功耗CMOS雙路運算放大器 |

| 文件頁數: | 8/16頁 |

| 文件大小: | 585K |

| 代理商: | LPC662 |

Application Hints

(Continued)

amps, due to the additional gain stage; however, when driv-

ing load resistance of 5 k

or less, the gain will be reduced

as indicated in the Electrical Characteristics. The op amp

can drive load resistance as low as 500

without instability.

COMPENSATING INPUT CAPACITANCE

Refer to the LMC660 or LMC662 datasheets to determine

whether or not a feedback capacitor will be necessary for

compensation and what the value of that capacitor would be.

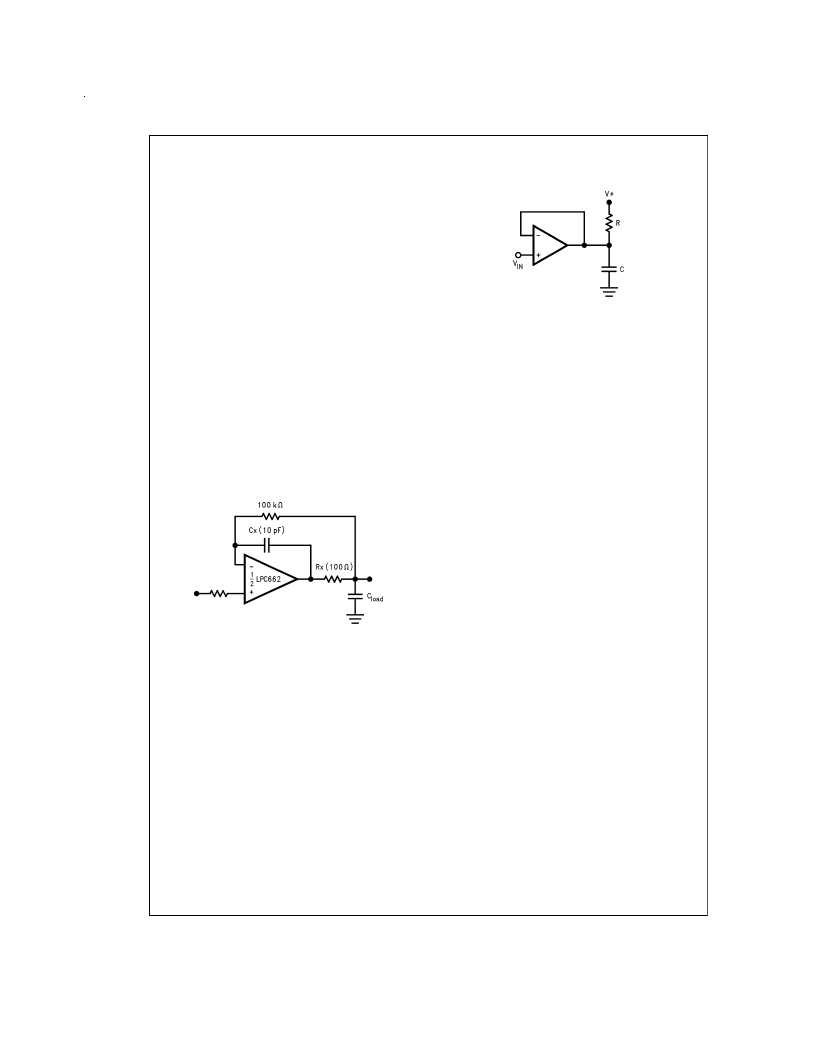

CAPACITIVE LOAD TOLERANCE

Like many other op amps, the LPC662 may oscillate when

its applied load appears capacitive. The threshold of oscilla-

tion varies both with load and circuit gain. The configuration

most sensitive to oscillation is a unity-gain follower. See the

Typical Performance Characteristics.

The load capacitance interacts with the op amp’s output re-

sistance to create an additional pole. If this pole frequency is

sufficiently low, it will degrade the op amp’s phase margin so

that the amplifier is no longer stable at low gains. The addi-

tion of a small resistor (50

to 100

) in series with the op

amp’s output, and a capacitor (5 pF to 10 pF) from inverting

input to output pins, returns the phase margin to a safe value

without interfering with lower-frequency circuit operation.

Thus, larger values of capacitance can be tolerated without

oscillation. Note that in all cases, the output will ring heavily

when the load capacitance is near the threshold for

oscillation.

Capacitive load driving capability is enhanced by using a

pull up resistor to V

+

Figure 3 Typically a pull up resistor

conducting 50 μA or more will significantly improve capaci-

tive load responses. The value of the pull up resistor must be

determined based on the current sinking capability of the

amplifier with respect to the desired output swing. Open loop

gain of the amplifier can also be affected by the pull up resis-

tor (see Electrical Characteristics).

PRINTED-CIRCUIT-BOARD LAYOUT

FOR HIGH-IMPEDANCE WORK

It is generally recognized that any circuit which must operate

with less than 1000 pA of leakage current requires special

layout of the PC board. When one wishes to take advantage

of the ultra-low bias current of the LPC662, typically less

than 0.04 pA, it is essential to have an excellent layout. For-

tunately, the techniques for obtaining low leakages are quite

simple. First, the user must not ignore the surface leakage of

the PC board, even though it may sometimes appear accept-

ably low, because under conditions of high humidity or dust

or contamination, the surface leakage will be appreciable.

To minimize the effect of any surface leakage, lay out a ring

of foil completely surrounding the LPC662’s inputs and the

terminals of capacitors, diodes, conductors, resistors, relay

terminals, etc. connected to the op-amp’s inputs. See Figure

4 To have a significant effect, guard rings should be placed

on both the top and bottom of the PC board. This PC foil

must then be connected to a voltage which is at the same

voltage as the amplifier inputs, since no leakage current can

flow between two points at the same potential. For example,

a PC board trace-to-pad resistance of 10

ohms, which is

normally considered a very large resistance, could leak 5 pA

if the trace were a 5V bus adjacent to the pad of an input.

This would cause a 100 times degradation from the

LPC662’s actual performance. However, if a guard ring is

held within 5 mV of the inputs, then even a resistance of

10

11

ohms would cause only 0.05 pA of leakage current, or

perhaps a minor (2:1) degradation of the amplifier’s perfor-

mance. See Figure 5a Figure 5b Figure 5c for typical con-

nections of guard rings for standard op-amp configurations.

If both inputs are active and at high impedance, the guard

can be tied to ground and still provide some protection; see

Figure 5d

DS010548-7

FIGURE 2. Rx, Cx Improve Capacitive Load Tolerance

DS010548-26

FIGURE 3. Compensating for Large

Capacitive Loads with A Pull Up Resistor

www.national.com

8

相關PDF資料 |

PDF描述 |

|---|---|

| LPC662AIM | Low Power CMOS Dual Operational Amplifier |

| LPC662AIN | Low Power CMOS Dual Operational Amplifier |

| LPC662AMD | Low Power CMOS Dual Operational Amplifier |

| LPC662IM | Low Power CMOS Dual Operational Amplifier |

| LPC662IN | Low Power CMOS Dual Operational Amplifier |

相關代理商/技術參數 |

參數描述 |

|---|---|

| LPC662AIM | 功能描述:運算放大器 - 運放 RoHS:否 制造商:STMicroelectronics 通道數量:4 共模抑制比(最小值):63 dB 輸入補償電壓:1 mV 輸入偏流(最大值):10 pA 工作電源電壓:2.7 V to 5.5 V 安裝風格:SMD/SMT 封裝 / 箱體:QFN-16 轉換速度:0.89 V/us 關閉:No 輸出電流:55 mA 最大工作溫度:+ 125 C 封裝:Reel |

| LPC662AIM/NOPB | 功能描述:運算放大器 - 運放 Low Power CMOS Dual Op Amp RoHS:否 制造商:STMicroelectronics 通道數量:4 共模抑制比(最小值):63 dB 輸入補償電壓:1 mV 輸入偏流(最大值):10 pA 工作電源電壓:2.7 V to 5.5 V 安裝風格:SMD/SMT 封裝 / 箱體:QFN-16 轉換速度:0.89 V/us 關閉:No 輸出電流:55 mA 最大工作溫度:+ 125 C 封裝:Reel |

| LPC662AIM/NOPB | 制造商:Texas Instruments 功能描述:Operational Amplifier (Op-Amp) IC |

| LPC662AIMX | 功能描述:運算放大器 - 運放 RoHS:否 制造商:STMicroelectronics 通道數量:4 共模抑制比(最小值):63 dB 輸入補償電壓:1 mV 輸入偏流(最大值):10 pA 工作電源電壓:2.7 V to 5.5 V 安裝風格:SMD/SMT 封裝 / 箱體:QFN-16 轉換速度:0.89 V/us 關閉:No 輸出電流:55 mA 最大工作溫度:+ 125 C 封裝:Reel |

| LPC662AIMX/NOPB | 功能描述:運算放大器 - 運放 RoHS:否 制造商:STMicroelectronics 通道數量:4 共模抑制比(最小值):63 dB 輸入補償電壓:1 mV 輸入偏流(最大值):10 pA 工作電源電壓:2.7 V to 5.5 V 安裝風格:SMD/SMT 封裝 / 箱體:QFN-16 轉換速度:0.89 V/us 關閉:No 輸出電流:55 mA 最大工作溫度:+ 125 C 封裝:Reel |

發布緊急采購,3分鐘左右您將得到回復。