- 您現在的位置:買賣IC網 > Datasheet目錄55 > MAX2365ETM+T (Maxim Integrated)IC TRANSMITTER QUAD 48TQFN-EP Datasheet資料下載

參數資料

| 型號: | MAX2365ETM+T |

| 廠商: | Maxim Integrated |

| 文件頁數: | 14/29頁 |

| 文件大小: | 460K |

| 描述: | IC TRANSMITTER QUAD 48TQFN-EP |

| 產品培訓模塊: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 標準包裝: | 2,500 |

| 頻率: | 900MHz |

| 應用: | 無線 LAN |

| 功率 - 輸出: | 9dBm |

| 電流 - 傳輸: | 90mA |

| 數據接口: | PCB,表面貼裝 |

| 天線連接器: | PCB,表面貼裝 |

| 電源電壓: | 2.7V ~ 3.3V |

| 工作溫度: | -40°C ~ 85°C |

| 封裝/外殼: | 48-WFQFN 裸露焊盤 |

| 包裝: | 帶卷 (TR) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁

Complete Dual-Band

Quadrature Transmitters

14 ______________________________________________________________________________________

Cascaded Performance

Tables 11 and 12 show the typical cascaded perfor-

mance for TDMA and W-CDMA systems.

3-Wire Interface

Figure 5 shows the 3-wire interface timing diagram. The

3-wire bus is SPI/QSPI/MICROWIRE compatible.

Electromagnetic

Compliance Considerations

Two major concepts should be employed to produce a

low-spur and EMC-compliant transmitter: minimize cir-

cular current-loop area to reduce H-field radiation. To

minimize circular current-loop area, bypass as close to

the part as possible and use the distributed capaci-

tance of a ground plane. To minimize voltage drops,

make V

CC

traces short and wide, and make RF traces

short.

Program only the necessary bits in any register to mini-

mize clock cycles. RC filtering can also be used to slow

the clock edges on the 3-wire interface, reducing high-

frequency spectral content. RC filtering also provides

for transient protection against IEC802 testing by shunt-

ing high frequencies to ground, while the series resis-

tance attenuates the transients for error-free operation.

The same applies to the logic input pins (SHDN,

TXGATE, IDLE).

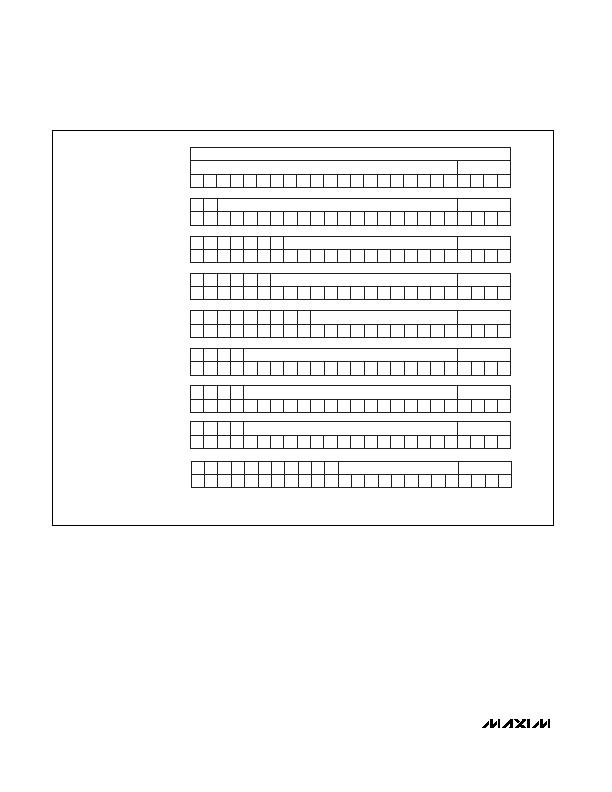

Figure 1. Register Configuration

MSB

24 BIT REGISTER

LSB

DATA 20 BITS

ADDRESS 4 BITS

B18

B16

B19

B17

B14

B12

B15

B13

B10

B8

B11

B9

B6

B4

B7

B5

B2

B0

B3

B1

A2

A0

A3

A1

RFM DIVIDE RATIO (18)

ADDRESS

X

B16

X

B17

B14

B12

B15

B13

B10

B8

B11

B9

B6

B4

B7

B5

B2

B0

B3

B1

0

0

0

0

RFM DIVIDE REGISTER

RFR DIVIDE RATIO (13)

ADDRESS

X

X

X

X

X

B12

X

X

B10

B8

B11

B9

B6

B4

B7

B5

B2

B0

B3

B1

0

1

0

0

RFR DIVIDE REGISTER

IFM DIVIDE RATIO (14)

ADDRESS

X

X

X

X

X

B12

X

B13

B10

B8

B11

B9

B6

B4

B7

B5

B2

B0

B3

B1

0

0

0

1

IFM DIVIDE REGISTER

IFR DIVIDE RATIO (11)

ADDRESS

X

X

X

X

X

X

X

X

B10

B8

X

B9

B6

B4

B7

B5

B2

B0

B3

B1

0

1

0

1

IFR DIVIDE REGISTER

OPERATION CONTROL BITS (16)

ADDRESS

X

X

X

X

B14

B12

B15

B13

B10

B8

B11

B9

B6

B4

B7

B5

B2

B0

B3

B1

1

0

0

0

CONTROL REGISTER

CONFIGURATION BITS (16)

ADDRESS

X

X

X

X

B14

B12

B15

B13

B10

B8

B11

B9

B6

B4

B7

B5

B2

B0

B3

B1

1

1

0

0

CONFIGURATION REGISTER

TEST REGISTER

CURRENT CONTROL REGISTER

X = DONT CARE

1

0

1

1

B1

B3

B0

B2

B5

B7

B4

B6

X

X

B8

X

X

X

X

X

X

X

X

X

ADDRESS

1

0

0

1

B1

B3

B0

B2

B5

B7

B4

B6

B9

B11

B8

B10

B13

B12

B15

X

X

X

X

ADDRESS

CURRENT CONTROL BITS (16)

B14

TEST BITS (9)

相關PDF資料 |

PDF描述 |

|---|---|

| MAX2369EGM+TD | IC TRANSMITTER QUAD 48QFN-EP |

| MAX2850ITK+ | TRANSMITTER MIMO 5GHZ 4CH 68TQFN |

| MAX7057ASE+T | IC TRANSMITTER ASK/FSK 16-SOIC |

| MBA-2060 | ANTENNA METROLOGY BICONICAL |

| MC33493ADTBER2 | IC RF TRANSMITTER UHF 14-TSSOP |

相關代理商/技術參數 |

參數描述 |

|---|---|

| MAX2366EGM | 制造商:Rochester Electronics LLC 功能描述: 制造商:Maxim Integrated Products 功能描述: |

| MAX2366EGM-D | 功能描述:射頻發射器 RoHS:否 制造商:Micrel 類型:ASK Transmitter 封裝 / 箱體:SOT-23-6 工作頻率:300 MHz to 450 MHz 封裝:Reel |

| MAX2366EGM-TD | 功能描述:射頻發射器 RoHS:否 制造商:Micrel 類型:ASK Transmitter 封裝 / 箱體:SOT-23-6 工作頻率:300 MHz to 450 MHz 封裝:Reel |

| MAX2366EVKIT | 功能描述:射頻開發工具 RoHS:否 制造商:Taiyo Yuden 產品:Wireless Modules 類型:Wireless Audio 工具用于評估:WYSAAVDX7 頻率: 工作電源電壓:3.4 V to 5.5 V |

| MAX2367EGM | 制造商:Rochester Electronics LLC 功能描述: 制造商:Maxim Integrated Products 功能描述: |

發布緊急采購,3分鐘左右您將得到回復。