- 您現在的位置:買賣IC網 > PDF目錄371035 > MC44007P (MOTOROLA INC) CHROMA 4 VIDEO PROCESSOR PDF資料下載

參數資料

| 型號: | MC44007P |

| 廠商: | MOTOROLA INC |

| 元件分類: | 消費家電 |

| 英文描述: | CHROMA 4 VIDEO PROCESSOR |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PDIP40 |

| 封裝: | PLASTIC, DIP-40 |

| 文件頁數: | 14/40頁 |

| 文件大小: | 491K |

| 代理商: | MC44007P |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

MC44002 MC44007

14

MOTOROLA ANALOG IC DEVICE DATA

Introduction

The following information describes the basic operation of

the MC44002/7 IC together with the MC44140 chroma delay

line. The MC44002/7 is a highly advanced circuit which

performs all the video processing, timebase and display

functions needed for a modern color TV. The device employs

analog circuitry but with the difference that all its advanced

features are under processor control, enabling external

filtering and potentiometer adjustments to be removed

completely. Sophisticated feedback control techniques have

been used throughout the design to ensure stable operating

conditions and the absence of drift with age.

The IC described herein is one of a new generation of TV

circuits, which make use of a serial data bus to carry out

control functions. Its revolutionary design concept permits a

level of integration and degree of flexibility never achieved

before. The MC44002/7 consists of a single bipolar VLSI chip

which uses a high density, high frequency, low voltage

process called MOSAIC 1.5. Contained within this single 40

pin package is all the circuitry needed for the video signal

processing, horizontal and vertical timebases and CRT

display control for today’s color TV. Furthermore, all the user

controls and manufacturer’s set-up adjustments are under

the control of the processor I2C bus, eliminating the need for

potentiometer controls. The MC44002/7 offers an enormous

variety of different options configurable in software, to cater

to virtually any video standard or circumstance commonly

met. The decoder section offers full multistandard capability,

able to handle PAL, SECAM (MC44002 only) and NTSC

standards with 4 matrix modes available. Practically all the

filtering is carried out onboard the IC by means of sampled

data filters, and requires no external components or

adjustment.

Digital Interface

One of the most important features of MC44002/7 is the

use of processor control to replace external potentiometer

and filter adjustments. Great flexibility is possible using

processor control, as each user can configure the software to

suit their individual application. The circuit operates on a

bidirectional serial data bus, based on the well known I2C

bus. This system is rapidly becoming a world standard for the

control of consumer equipment.

I2C Bus

It is not within the scope of this data sheet to describe in

detail the functioning of the I2C bus. Basically, the I2C bus is

a two-wire bidirectional system consisting of a clock and a

serial data stream. The write cycle consists of 3 bytes of data

and 3 acknowledge bits. The first byte is the Chip Address,

the second the Sub-address to identify the location in the

memory, and the third byte is the data. When the address’

Read/Write bit is high, the second and third bytes are used to

transmit status flags back to the MCU.

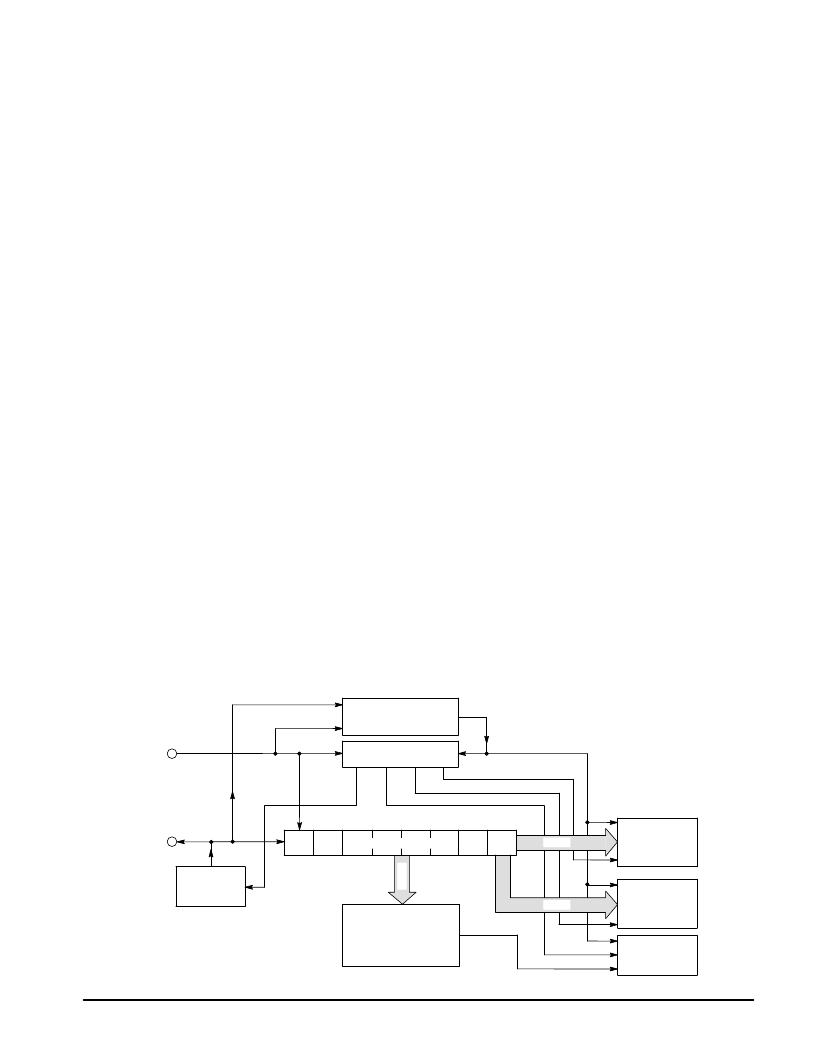

Figure 6 shows a block diagram of the MC44002/7 Bus

Interface/Decoder. To begin with, the start bit is recognized

by means of the data going low during CLK high. This causes

the Counter and all the latches to be reset. For a write

operation, the Write address ($88) is read into the Shift

Register. If the correct address is identified, the Chip Address

Latch is set and at CLK 9 an acknowledge is sent.

The second byte is now read into the Shift Register and is

used to select the Sub-address. At CLK 18 a Sub-address

Enable is sent to the memory to allow the Data in the register

to be changed. Also, at CLK 18 another acknowledge is sent.

The third byte is now read into the Shift Register and the

Data bussed into the memory. The Data in the Sub-address

location already selected is then altered. A third acknowledge

is sent at CLK 27 to complete the cycle.

A Read address ($89) indicates that the MCU wants to

read the MC44002/7 status flags. In this instance, the

Read/Write Latch is set, causing the Memory Enable and

Subaddress Enable to be inhibited, and the flags to be written

onto the data line. Two of the status flags are permanently

wired one-high and one-low (O.K. and Fault), to provide a

check on the communication medium between the

MC44002/7 and the MCU.

At start-up the Counter is automatically reset and the Data

for each Sub-address is read in from the MCU. Only after the

entire memory contents have been transmitted, is Data 00

sent to register 00 to start the Horizontal Drive.

The MC44002/7 needs the full 27 clock cycles, or a stop

condition, to properly release the I2C bus.

4

Figure 6. I2C Bus Interface and Decoder

8-Bit Shift Register

Read/Write

Latch

Chip-Address

Latch

Sub-Address

Latches

Memory &

Sub-Address

Decoding

Acknowledge

Data

Clock

Clock Counter

Reset

Start-Bit

Recognition

5

8

8-Bit

8-Bit

相關PDF資料 |

PDF描述 |

|---|---|

| MC44007 | CHROMA 4 VIDEO PROCESSOR |

| MC44035FTB | MULTISTANDARD VIDEO SIGNAL PROCESSOR WITH INTEGRATED CHROMA DELAY LINE |

| MC44030FTB | MULTISTANDARD VIDEO SIGNAL PROCESSOR WITH INTEGRATED CHROMA DELAY LINE |

| MC44030P | MULTISTANDARD VIDEO SIGNAL PROCESSOR WITH INTEGRATED CHROMA DELAY LINE |

| MC44035P | MULTISTANDARD VIDEO SIGNAL PROCESSOR WITH INTEGRATED CHROMA DELAY LINE |

相關代理商/技術參數 |

參數描述 |

|---|---|

| MC4401 | 制造商:SHENZHENFREESCALE 制造商全稱:ShenZhen FreesCale Electronics. Co., Ltd 功能描述:P-Channel 30-V (D-S) MOSFET Low thermal impedance |

| MC44011 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Chroma 4 Multistandard Video Processor |

| MC44011FB | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:BUS CONTROLLED MULTISTANDARD VIDEO PROCESSOR |

| MC44011FN | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Chroma 4 Multistandard Video Processor |

| MC4403 | 制造商:SHENZHENFREESCALE 制造商全稱:ShenZhen FreesCale Electronics. Co., Ltd 功能描述:P-Channel 20-V (D-S) MOSFET High performance trench technology |

發布緊急采購,3分鐘左右您將得到回復。