- 您現在的位置:買賣IC網 > PDF目錄371044 > MC68360RC25V (MOTOROLA INC) QUad Integrated Communications Controller Users Manual PDF資料下載

參數資料

| 型號: | MC68360RC25V |

| 廠商: | MOTOROLA INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | QUad Integrated Communications Controller Users Manual |

| 中文描述: | RISC MICROCONTROLLER, CPGA241 |

| 封裝: | PGA-241 |

| 文件頁數: | 7/28頁 |

| 文件大小: | 159K |

| 代理商: | MC68360RC25V |

第1頁第2頁第3頁第4頁第5頁第6頁當前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

MOTOROLA

MC68360 USER’S MANUAL ERRATA

7

11. Corrections for RCNT—Refresh Counter Period Description.

On page 6-64, section 6.13.1, make the following corrections:

a) ‘RFCNT’ in the equation should be ‘RCNT’.

b) ‘24 (decimal)’ in the example should be ‘23 (decimal)’.

c) ‘24 / (25 MHz / 16)’ in the example should be ‘(23 + 1) / (25 MHz / 16)’.

12. Typo on Global Memory Register.

On page 6-65, section 6.13.1, the following should replace the definition of PGS2-PGS0:

PGS2–PGS0—Page Size

This attribute determines the page size and AMUX for the DRAM controller (see Table 6-

9). For multiplexing information see Table 6-8 on page 6-59. The page size is the smallest

DRAM size the user needs to support page mode capability.

Delay Write QUICC Bit Definition.

On page 6-66, section 6.13.1, the description of the DWQ bit was not clear. The bit definition

should be replaced as follows:

DWQ—Delay Write for QUICC (DRAM Bank Only)

This attribute is used to add a clock to the assertion and negation of the CAS signal on

DRAM page hit write cycles. The write cycle lasts one additional clock in this case. This

attribute is applicable to an internal QUICC master and to an external MC68030/QUICC.

0 = Reads and writes are the same length.

1 = Add one clock to write cycles for DRAM banks.

NOTE

This bit must be set by the user if page mode is enabled for this

DRAM bank (PGME = 1), and when a zero wait state DRAM is

implemented by setting TCYC to be zero. If this is not done the

DRAM may latch invalid data during writes.

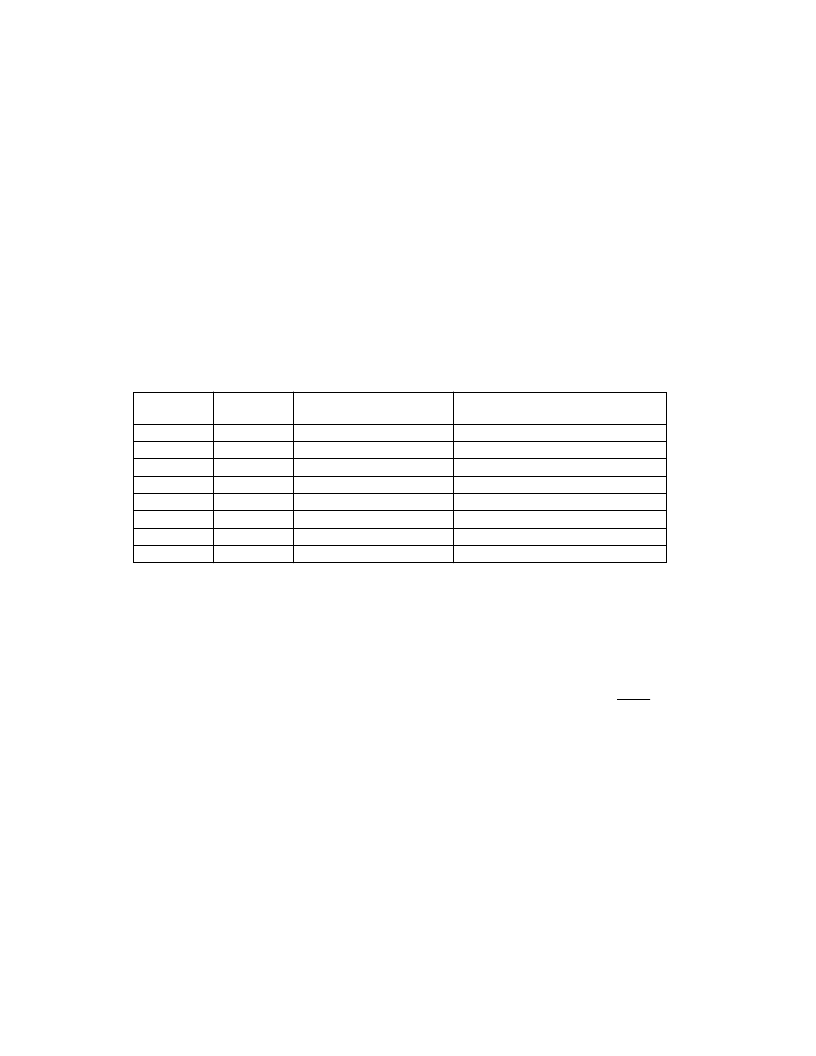

Table 6-9. DRAM Page Size

Address Lines Compared

for Page Hit or Miss

A10-25(32), A9-25(16)

A11-25(32), A10-25(16)

A11-25(32), A10-25(16)

A12-25(32), A11-25(16)

A12-25(32), A11-25(16)

A13-25(32), A12-25(16)

A13-25(32), A12-25(16)

A14-25(32), A13-25(16)

DRAM Size

PGS2-PGS0

# Address/Page in Page Compare

128k

256k

512k

1M

2M

4M

8M

16M

000

001

010

011

100

101

110

111

256 Addresses

512 Addresses

512 Addresses

1024 Addresses

1024 Addresses

2048 Addresses

2048 Addresses

4096 Addresses

F

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

.

相關PDF資料 |

PDF描述 |

|---|---|

| MC68360RC33 | QUad Integrated Communications Controller Users Manual |

| MC68360ZP25 | QUad Integrated Communications Controller Users Manual |

| MC68040 | Errata and Added Information to MC68360 Quad Integrated Communication Controller User Manual Rev 1 |

| MC68360 | 32-Bit Microprocessor(32位微處理器) |

| MC6840 | Programmable Timer Module(PTM) |

相關代理商/技術參數 |

參數描述 |

|---|---|

| MC68360RC33 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:QUad Integrated Communications Controller Users Manual |

| MC68360RC33L | 功能描述:微處理器 - MPU QUICC SIM 4SCC RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數據總線寬度:32 bit 最大時鐘頻率:536 MHz 程序存儲器大小:32 KB 數據 RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MC68360TUT | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:TUTORIAL A QUICC-START |

| MC68360UM | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:MC68360 QUad Integrated Communication Controller (QUICCa?¢) |

| MC68360UM/AD | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:MC68360 QUad Integrated Communication Controller |

發布緊急采購,3分鐘左右您將得到回復。