- 您現在的位置:買賣IC網 > PDF目錄361075 > NB4N441 (ON SEMICONDUCTOR) 3.3V Serial Input MultiProtocol PLL Clock Synthesizer, Differential LVPECL Output(3.3V串行輸入多協議PLL時鐘合成器, 差分LVPECL輸出) PDF資料下載

參數資料

| 型號: | NB4N441 |

| 廠商: | ON SEMICONDUCTOR |

| 英文描述: | 3.3V Serial Input MultiProtocol PLL Clock Synthesizer, Differential LVPECL Output(3.3V串行輸入多協議PLL時鐘合成器, 差分LVPECL輸出) |

| 中文描述: | 3.3串行輸入多協議PLL時鐘合成器,差分LVPECL輸出電壓(3.3V串行輸入多協議PLL的時鐘合成器,差分LVPECL的輸出) |

| 文件頁數: | 3/12頁 |

| 文件大小: | 168K |

| 代理商: | NB4N441 |

NB4N441

http://onsemi.com

3

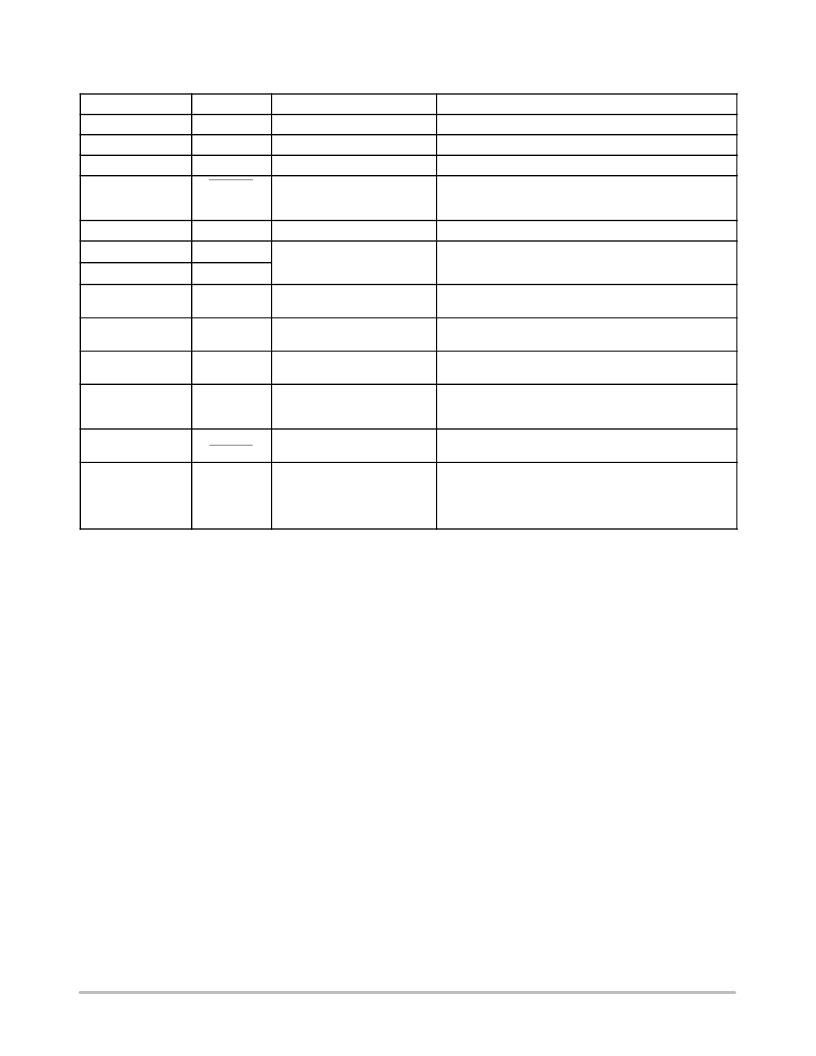

Table 1. PIN DESCRIPTION

Pin

Name

I/O

Description

11, 12, 13, 24

V

CC

Power Supply

Positive supply voltage.

3

VCC_PLL

PLL Power Supply

Positive supply voltage for the PLL.

1, 6, 9, 18, 19

GND

Ground

Ground.

20

LOCKED

LVTTL Lock Output

When Low, this output provides indication that the PLL is

locked and the device is in proper operating mode. When

High, the PLL is out of lock.

2, 4, 5, 10, 14

NC

No Connect.

8

CLK / XTAL1,

LVTTL/LVCMOS Single Ended

Clock or XTAL Inputs

The crystal is connected between the XTAL1 and XTAL2 pin.

If driving single

ended, use XTAL1 and leave XTAL2

floating.

7

XTAL2

15

SLOAD**

LVTTL / LVCMOS,

Serial Load Input

Serial Load.

16

SDATA**

LVTTL / LVCMOS

Serial Data Input

Serial Data Input.

17

SCLOCK**

LVTTL / LVCMOS

Serial Clock Input

Serial Clock Input.

21

OE*

LVTTL Input

Synchronous Output Enable. When OE is HIGH or left

OPEN, the outputs are enabled. When OE is LOW, the

outputs are disabled.

22, 23

CLKOUT

CLKOUT

LVPECL Output

Differential LVPECL Clock Outputs, Typically terminated with

50 resistor to VCC – 2.0 V.

EP

The Exposed Pad on the 24 pin QFN package bottom is

thermally connected to the die for improved heat transfer out

of package. The pad is not electrically connected to the die,

but is recommended to be electrically connected to GND on

the PC board.

*Pins will default HIGH when left Open

**Pins will default LOW when left Open

相關PDF資料 |

PDF描述 |

|---|---|

| NB4N840M | 3.3V 2.7Gb/s Dual Differential Clock/Data 2 x 2 Crosspoint Switch with CML Output and Internal Termination(帶CML輸出和內部終端的3.3V,2.7Gb/s雙差分時鐘/數據2x2交點開關) |

| NB6L11 | 2.5V / 3.3V MULTILEVEL INPUT TO DIFFERENTIAL LVPECL/LVNECL 1:2 CLOCK OR DATA FANOUT BUFFER / TRANSLATOR |

| NB6L11D | 2.5V / 3.3V MULTILEVEL INPUT TO DIFFERENTIAL LVPECL/LVNECL 1:2 CLOCK OR DATA FANOUT BUFFER / TRANSLATOR |

| NB6L11DR2 | 2.5V / 3.3V MULTILEVEL INPUT TO DIFFERENTIAL LVPECL/LVNECL 1:2 CLOCK OR DATA FANOUT BUFFER / TRANSLATOR |

| NB6L11DT | 2.5V / 3.3V MULTILEVEL INPUT TO DIFFERENTIAL LVPECL/LVNECL 1:2 CLOCK OR DATA FANOUT BUFFER / TRANSLATOR |

相關代理商/技術參數 |

參數描述 |

|---|---|

| NB4N441_07 | 制造商:ONSEMI 制造商全稱:ON Semiconductor 功能描述:3.3V Serial Input MultiProtocol PLL Clock Synthesizer, Differential LVPECL Output |

| NB4N441MNG | 功能描述:鎖相環 - PLL MLTPRTCL PLL CLK SYN RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| NB4N441MNGEVB | 功能描述:BOARD EVAL NB4N441MNG RoHS:是 類別:編程器,開發系統 >> 評估演示板和套件 系列:* 產品培訓模塊:Obsolescence Mitigation Program 標準包裝:1 系列:- 主要目的:電源管理,電池充電器 嵌入式:否 已用 IC / 零件:MAX8903A 主要屬性:1 芯鋰離子電池 次要屬性:狀態 LED 已供物品:板 |

| NB4N441MNR2G | 功能描述:鎖相環 - PLL MLTPRTCL PLL CLK SYN RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| NB4N507A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:3.3V/5V, 50 MHz to 200 MHz PECL Clock Synthesizer |

發布緊急采購,3分鐘左右您將得到回復。