- 您現在的位置:買賣IC網 > PDF目錄382370 > PA7536J-15 ASIC PDF資料下載

參數資料

| 型號: | PA7536J-15 |

| 英文描述: | ASIC |

| 中文描述: | 專用集成電路 |

| 文件頁數: | 5/10頁 |

| 文件大小: | 219K |

| 代理商: | PA7536J-15 |

5

04-02-052D

Commercial/Industrial

PEEL

Array Development Support

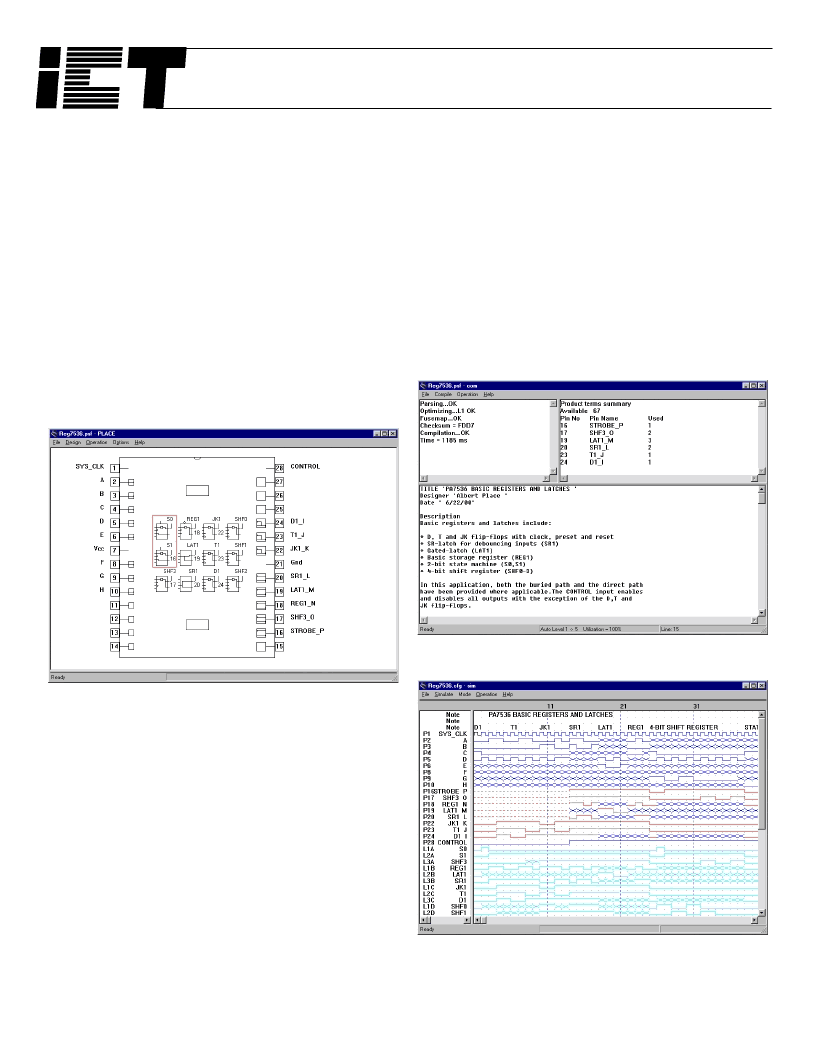

Development support for PEEL

Arrays is provided by

ICT and manufacturers of popular development tools. ICT

offers the powerful WinPLACE Development Software (free

to qualified PLD designers). The WinPLACE software

includes an architectural editor, logic compiler, waveform

simulator, documentation utility and a programmer

interface. The WinPLACE editor graphically illustrates and

controls the PEEL

Array

’

s architecture, making the

overall design easy to understand, while allowing the

effectiveness of boolean logic equations, state machine

design and truth table entry. The WinPLACE compiler

performs logic transformation and reduction, making it

possible to specify equations in almost any fashion and fit

the most logic possible in every design. WinPLACE also

provides a multi-level logic simulator allowing external and

internal signals to be simulated and analyzed via a

waveform display.(See Figure 12, Figure 13 and Figure 14)

Figure 12 - WinPLACE Architectural Editor for

PA7536

PEEL

Array development is also supported by popular

development tools, such as ABEL and CUPL, via ICT

’

s

PEEL

Array fitters. A special smart translator utility adds

the capability to directly convert JEDEC files for other

devices into equivalent JEDEC files for pin-compatible

PEEL

Arrays.

Programming

PEEL

Arrays are EE-reprogrammable in all package

types, plastic-DIP, PLCC, SOIC and TSSOP. This makes

them an ideal development vehicle for the lab. EE-

reprogrammability is also useful for production, allowing

unexpected changes to be made quickly and without

waste. Programming of PEEL

Arrays is supported by

popular third party programmers.

Design Security and Signature Word

The PEEL

Arrays provide a special EEPROM security bit

that prevents unauthorized reading or copying of designs.

Once set, the programmed bits of the PEEL

Arrays

cannot be accessed until the entire chip has been

electrically

erased.

Another

signature word, allows a user-definable code to be

programmed into the PEEL

Array. The code can be read

back even after the security bit has been set. The signature

word can be used to identify the pattern programmed in the

device or to record the design revision.

programming

feature,

Figure 13 - WinPLACE LCC and IOC screen

Figure 14 - WinPLACE simulator screen

相關PDF資料 |

PDF描述 |

|---|---|

| PA7 | Analog IC |

| PAC21S07AS | Analog IC |

| PACK-1 | |

| PACKAGE | Package diagrams and shipping information |

| PACKAGESANDPACKING | Packages and Packing - Trays Part 12 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| PA7536J-15L | 功能描述:SPLD - 簡單可編程邏輯器件 14 Input 12 I/O 15ns RoHS:否 制造商:Texas Instruments 邏輯系列:TICPAL22V10Z 大電池數量:10 最大工作頻率:66 MHz 延遲時間:25 ns 工作電源電壓:4.75 V to 5.25 V 電源電流:100 uA 最大工作溫度:+ 75 C 最小工作溫度:0 C 安裝風格:Through Hole 封裝 / 箱體:DIP-24 |

| PA7536JI-15 | 功能描述:SPLD - 簡單可編程邏輯器件 14 INP 12 I/O 15ns RoHS:否 制造商:Texas Instruments 邏輯系列:TICPAL22V10Z 大電池數量:10 最大工作頻率:66 MHz 延遲時間:25 ns 工作電源電壓:4.75 V to 5.25 V 電源電流:100 uA 最大工作溫度:+ 75 C 最小工作溫度:0 C 安裝風格:Through Hole 封裝 / 箱體:DIP-24 |

| PA7536JI-15L | 功能描述:SPLD - 簡單可編程邏輯器件 14 Input 12 I/O 15ns RoHS:否 制造商:Texas Instruments 邏輯系列:TICPAL22V10Z 大電池數量:10 最大工作頻率:66 MHz 延遲時間:25 ns 工作電源電壓:4.75 V to 5.25 V 電源電流:100 uA 最大工作溫度:+ 75 C 最小工作溫度:0 C 安裝風格:Through Hole 封裝 / 箱體:DIP-24 |

| PA7536P-15 | 功能描述:SPLD - 簡單可編程邏輯器件 14 INP 12 I/O 15ns RoHS:否 制造商:Texas Instruments 邏輯系列:TICPAL22V10Z 大電池數量:10 最大工作頻率:66 MHz 延遲時間:25 ns 工作電源電壓:4.75 V to 5.25 V 電源電流:100 uA 最大工作溫度:+ 75 C 最小工作溫度:0 C 安裝風格:Through Hole 封裝 / 箱體:DIP-24 |

| PA7536P-15L | 功能描述:SPLD - 簡單可編程邏輯器件 14 Input 12 I/O 15ns RoHS:否 制造商:Texas Instruments 邏輯系列:TICPAL22V10Z 大電池數量:10 最大工作頻率:66 MHz 延遲時間:25 ns 工作電源電壓:4.75 V to 5.25 V 電源電流:100 uA 最大工作溫度:+ 75 C 最小工作溫度:0 C 安裝風格:Through Hole 封裝 / 箱體:DIP-24 |

發布緊急采購,3分鐘左右您將得到回復。