- 您現在的位置:買賣IC網 > PDF目錄361236 > Q67100-H3525 (SIEMENS AG) 4 Kbit 512 x 8 bit Serial CMOS EEPROMs, I2C Synchronous 2-Wire Bus, Page Protection Mode PDF資料下載

參數資料

| 型號: | Q67100-H3525 |

| 廠商: | SIEMENS AG |

| 英文描述: | 4 Kbit 512 x 8 bit Serial CMOS EEPROMs, I2C Synchronous 2-Wire Bus, Page Protection Mode |

| 中文描述: | 4千位512 × 8位串行CMOS EEPROM的,I2C同步2線巴士,頁面保護模式 |

| 文件頁數: | 1/53頁 |

| 文件大小: | 418K |

| 代理商: | Q67100-H3525 |

當前第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁

HYB 39S64400/800/160BT(L)

64-MBit Synchronous DRAM

Data Book

1

12.99

The HYB 39S64400/800/160BT are four bank Synchronous DRAM’s organized as

4 banks

×

4MBit

×

4, 4 banks

×

2 MBit

×

8 and 4 banks

×

1 Mbit

×

16 respectively. These synchron-

ous devices achieve high speed data transfer rates by employing a chip architecture that prefects

multiple bits and then synchronizes the output data to a system clock. The chip is fabricated using

the Infineon advanced 0.2

μ

m 64 MBit DRAM process technology.

The device is designed to comply with all JEDEC standards set for Synchronous DRAM products,

both electrically and mechanically. All of the control, address, data input and output circuits are

synchronized with the positive edge of an externally supplied clock.

Operating the four memory banks in an interleave fashion allows random access operation to occur

at higher rates than is possible with standard DRAMs. A sequential and gapless data rate is

possible depending on burst length, CAS latency and speed grade of the device.

Auto Refresh (CBR) and Self Refresh operation are supported. These devices operates with a

single 3.3 V

±

0.3 V power supply and are available in TSOPII packages.

High Performance:

Fully Synchronous to Positive Clock Edge

0 to 70

°

C operating temperature

Four Banks controlled by BA0 & BA1

Programmable CAS Latency: 2, 3

Programmable Wrap Sequence: Sequential

or Interleave

Programmable Burst Length: 1, 2, 4, 8

Full page (optional) for sequential wrap

around

Multiple Burst Read with Single Write

Operation

Automatic and Controlled Precharge

Command

Data Mask for Read/Write Control (x4, x8)

Data Mask for Byte Control (x16)

Auto Refresh (CBR) and Self Refresh

Suspend Mode and Power Down Mode

4096 Refresh Cycles / 64 ms

Random Column Address every CLK

(1-N Rule)

Single 3.3 V

±

0.3 V Power Supply

LVTTL Interface

Plastic Packages:

P-TSOPII-54 400mil width (x4, x8, x16)

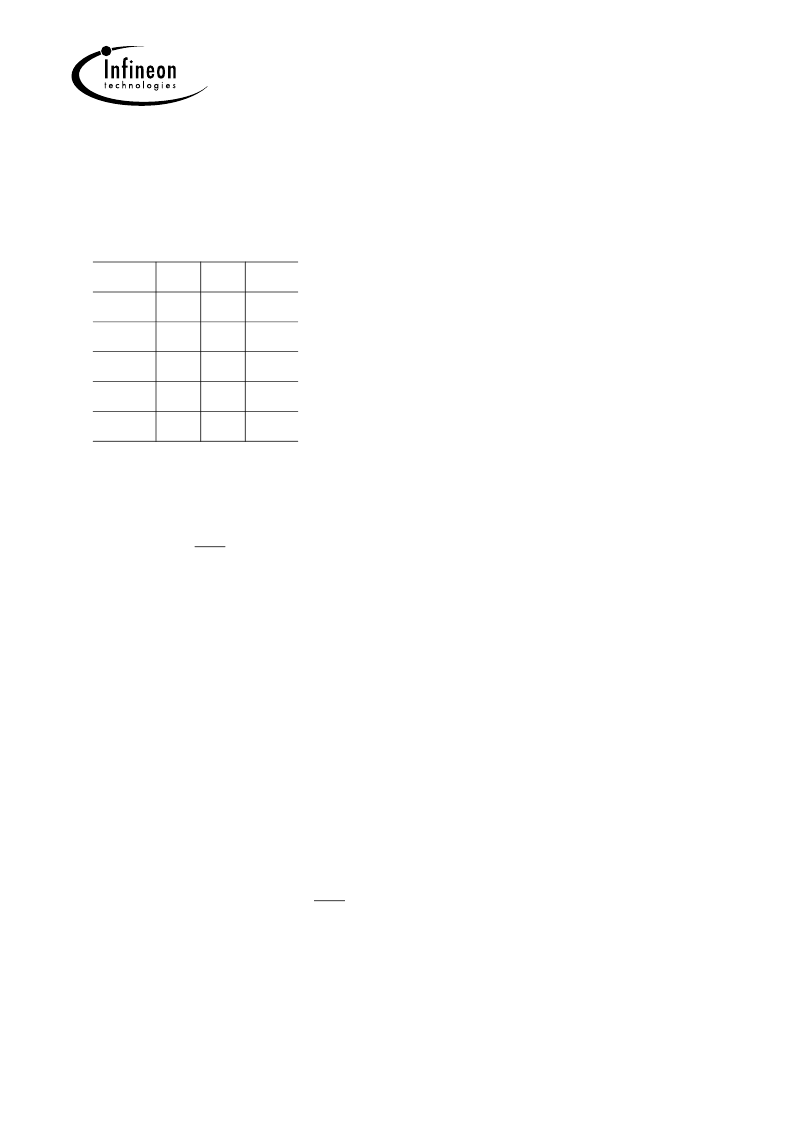

-7.5 version for PC133 3-3-3 application

-8 version for PC100 2-2-2 applications

-7.5

-8

Units

f

CKMAX

133

125

MHz

t

CK3

7.5

8

ns

t

AC3

5.4

6

ns

t

CK2

10

10

ns

t

AC2

6

6

ns

64-MBit Synchronous DRAM

相關PDF資料 |

PDF描述 |

|---|---|

| Q67100-H3526 | 4 Kbit 512 x 8 bit Serial CMOS EEPROMs, I2C Synchronous 2-Wire Bus, Page Protection Mode |

| Q67100-H3527 | 4 Kbit 512 x 8 bit Serial CMOS EEPROMs, I2C Synchronous 2-Wire Bus, Page Protection Mode |

| Q67100-H3528 | 4 Kbit 512 x 8 bit Serial CMOS EEPROMs, I2C Synchronous 2-Wire Bus |

| Q67100-H3529 | 4 Kbit 512 x 8 bit Serial CMOS EEPROMs, I2C Synchronous 2-Wire Bus |

| Q67100-H3530 | 4 Kbit 512 x 8 bit Serial CMOS EEPROMs, I2C Synchronous 2-Wire Bus, Page Protection Mode |

相關代理商/技術參數 |

參數描述 |

|---|---|

| Q67100-H3526 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:4 Kbit 512 x 8 bit Serial CMOS EEPROMs, I2C Synchronous 2-Wire Bus, Page Protection Mode |

| Q67100-H3527 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:4 Kbit 512 x 8 bit Serial CMOS EEPROMs, I2C Synchronous 2-Wire Bus, Page Protection Mode |

| Q67100-H3528 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:4 Kbit 512 x 8 bit Serial CMOS EEPROMs, I2C Synchronous 2-Wire Bus |

| Q67100-H3529 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:4 Kbit 512 x 8 bit Serial CMOS EEPROMs, I2C Synchronous 2-Wire Bus |

| Q67100-H3530 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:4 Kbit 512 x 8 bit Serial CMOS EEPROMs, I2C Synchronous 2-Wire Bus, Page Protection Mode |

發布緊急采購,3分鐘左右您將得到回復。